ΕΡΓΑΣΤΗΡΙΟ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ (2025-2026) (ΕCE333)

Σύνδεσμοι

| Γενικοί σύνδεσμοι |

|---|

| ECE-333 | Digital Circuits Design Lab | Verilog HDL, Quick Reference Guide by Sutherland HDL Inc. | Verilog HDL, Quick Reference by ASIC WORLD | Verilog HDL, Verilog Tutorial by ChipVerify A blog for students & engineers to know more about chip design and verification, languages and methodologies. | Online Xilinx / AMD Documentation Associated Documentation material for course and lab assignments:

|

| Κατηγορίες συνδέσμων | |||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Spartan 7 Boolean Board| FPGA | |||||||||||||||||||||||||

| Xilinx EDA Tools, Flows & Methodologies | |||||||||||||||||||||||||

| Vivado Design Suite | Hardware Developer

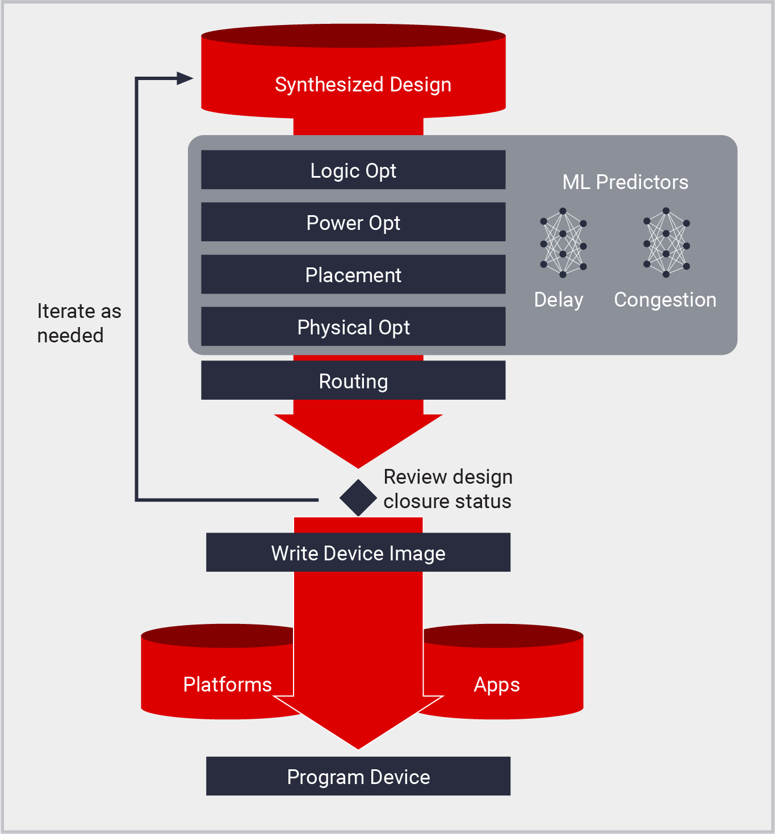

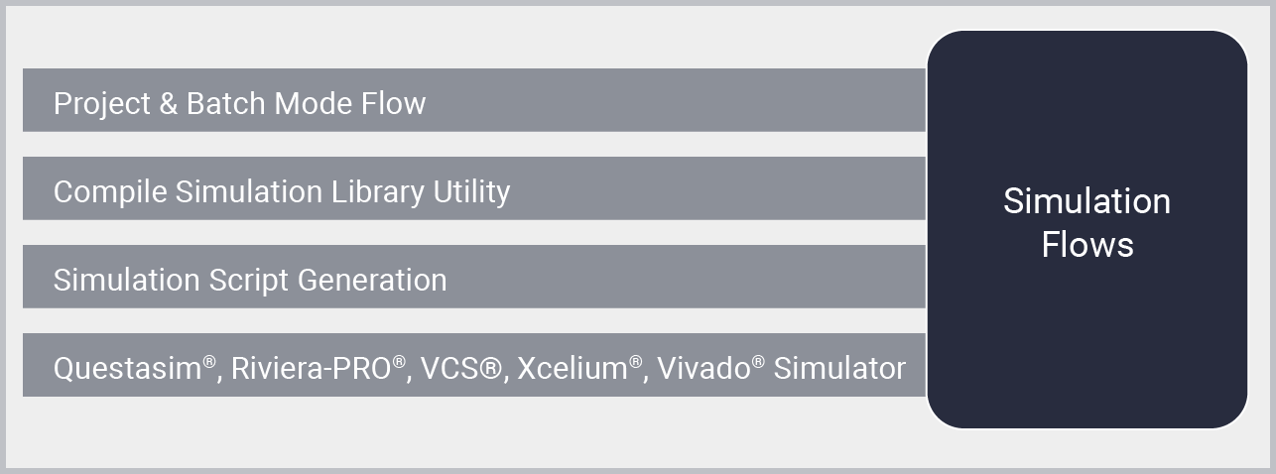

Overview (QuickTake video)Vivado Design Suite is a software suite produced by Xilinx for synthesis and analysis of HDL designs, supersending Xilinx ISE with additional features for System on-a Chip (SoC) develpoment and High-Level Synthesis (HLS). It is an Integrated Design Enviroment (IDE) with system-to-IC level tools built on a shared scalable data model and a common debug enviroment. Vivado includes Electronic System Level (ESL) design tools for synthesising and verifying C-based algorithmic IP, standards based packaging of both algorithmoc and RTL IP for reuse; standard based IP stitching and systems integration of all types of system building blocks; and the verification of blocks and system High-Level DesignVivado IP Integrator provides a graphical and Tcl-based, correct-by construction design development flow. Working at the interface level, design teams can rapidly assemble complex systems that leverage IP created with Vitis™ HLS, Vitis Model Composer, Xilinx IP, Alliance Member IP as well as your own IP. By leveraging the combination of newly improved Vivado IPI and HLS, customers are saving up to 15X in development costs versus an RTL approach. VerificationMeeting the verification challenges of today’s complex devices requires multitudes of tools and technologies at various levels of design. Vivado® Suite delivers these tools and technologies in a cohesive environment for accelerated verification of block- and chip-level designs. | Xilinx Developer Site Whether you are a software developer, hardware developer, or AI scientist, we have you covered with adaptable compute silicon and software platforms to power your innovation

Design HubsDesign Hubs make it easy to learn about specific design tasks by providing introductory material, key concepts, and FAQs along with quick access to the appropriate documentation, videos, and support resources for the task at hand. BoardsFrom concept to production, Xilinx FPGA and SoC boards, System-on-Modules, and Alveo Data Center accelerator cards provide you with hardware platforms to speed your development time, enhance your productivity, and accelerate your time to market. Whether you need an evaluation board to begin development or want to speed time-to-market and lower risk with production data center accelerator cards or System-on-Modules, Xilinx and its ecosystem partners offer the industry’s most comprehensive set of hardware platforms to help speed your time-to-revenue. Intellectual PropertyXilinx and our Partners have a rich library of Intellectual Property (IP), to help you get to market faster. Our IP goes through a vigorous test and validation effort to help you have success the first time. Beyond a simple library of cores we provide other solutions to help your productivity. IP Integrator is a GUI which enables rapid connection of IP which is enabled by a common user interface that is AXI based. This can reduce the design effort by months. We also have IP Subsystems that integrate multiple IP into one solution. Why generate a DMA and PCIe core, when we can deliver an IP Subsystem that does this for you. We have many other Subsystems too. Why worry about peripheral interfaces? Let us help you get to market faster. Focus on your application design. Our IP Solutions are designed to make you more productive.

| Xilinx University Program

The Xilinx University Program (XUP) enables the use of Xilinx FPGA and Zynq SoC tools and technologies for academic teaching and research. Benifits for Students:

| |||||||||||||||||||||||

| Other Generic Usefull Links | |||||||||||||||||||||||||

|

Related/Suggested Course Books A list of related and/or suggested course books. Several are provided by eudoxus platform. | |||||||||||||||||||||||||

Ψηφιακή Σχεδίαση, 6η Έκδοση: Με Εκτενή Παρουσίαση των Verilog, VHDL και SystemVerilog | Morris Mano, Michael Ciletti ΠεριγραφήΤο ακροατήριο στο οποίο απευθύνεται το βιβλίο είναι ευρύ και περιλαμβάνει σπουδαστές πεδίων όπως η ηλεκτρονική μηχανική, η μηχανική υπολογιστών και η επιστήμη των υπολογιστών. Μια καθαρή και προσιτή προσέγγιση στα βασικά εργαλεία, έννοιες και εφαρμογές της λογικής σχεδίασης. Η παρούσα αναθεωρημένη έκδοση του κλασσικού, καθιερωμένου βιβλίου «Ψηφιακή Σχεδίαση» διδάσκει τις βασικές έννοιες με απλό και προσιτό τρόπο. Το εγχειρίδιο παρουσιάζει τα βασικά εργαλεία του σχεδιασμού ψηφιακών κυκλωμάτων και παρέχει διαδικασίες κατάλληλες για μια πληθώρα ψηφιακών εφαρμογών. Όπως και οι προηγούμενες εκδόσεις, η παρούσα έκδοση υποστηρίζει μια πολυμορφική, πολυτροπική προσέγγιση στη διαδικασία της μάθησης, εστιάζοντας στην ψηφιακή σχεδίαση, ανεξάρτητα από την γλώσσα που χρησιμοποιείται. Αναγνωρίζοντας ότι οι τρεις κοινές γλώσσες - Verilog, VHDL, και SystemVerilog - παίζουν οι καθεμία το ρόλο τους στον σχεδιασμό των σύγχρονων ψηφιακών συσκευών, η 6η έκδοση προσφέρει παράλληλες μεθόδους παρουσίασης πολλαπλών γλωσσών, αλλά επιτρέπει και την εστίαση σε μία, επιλεγμένη γλώσσα.

| Ψηφιακή Σχεδίαση, 3η Έκδοση: Αρχές και Πρακτικές | John F. Wakerly ΠεριγραφήΑυτό το πρόσφατα αναθεωρημένο βιβλίο συνδυάζει την ακαδημαϊκή ακρίβεια με την πρακτική πείρα σε μια έγκυρη εισαγωγή ως προς τις βασικές αρχές της ψηφιακής σχεδίασης και των πρακτικών απαιτήσεων, τόσο για συστήματα σε επίπεδο πλακέτας όσο και σε συστήματα VLSI. Το βιβλίο καλύπτει τα βασικά δομικά υλικά της ψηφιακής σχεδίασης σε διάφορα αφαιρετικά επίπεδα, από τις πύλες CMOS μέχρι τις γλώσσες περιγραφής υλικού. Σε καθένα από τα επίπεδα αυτά αναλύονται οι σημαντικές λειτουργίες όπως οι πύλες, οι αποκωδικοποιητές, οι πολυπλέκτες, τα κυκλώματα φλιπ-φλοπ, οι καταχωρητές, και οι μετρητές.

| HDL Chip Design: A Practical Guide for Designing, Synthesizing & Simulating ASICs & FPGAs Using VHDL or Verilog | Douglas J. Smith Editorial Reviews Arthur C. Clarke once wrote that any sufficiently advanced civilization would possess seemingly magical powers to a lesser-advanced one. Technology, and in particular computer technology, has and always will present a Janus head to the world. While delivering enormous capability and freedom, the instrumentality by which that freedom is delivered becomes even more arcane and obscurantist to the users of that technology. The backyard auto mechanic is an artifact. We are all, including most mechanics, relegated to simply filling the gas tank, changing the oil or replacing the occasional black box. And what of those practitioners of these arcane arts, who in designing and building the devices which channel electrons to the exacting demands of industry and consumers seem to take on almost a mantle of priesthood? Any priesthood needs a catechism, and Douglas J. Smith's HDL Chip Design might well fit that role. This publication is designed as an introduction to and reference on using the two industry standard hardware description languages (HDL's) VDHL and Verilog to design, simulate and synthesize Applications-Specific Integrated Circuits (ASIC) and Field Programmable Gate-Arrays (FPGA). Emphasis for modeling is at the RT (register transfer) level, using a top-down design method. This reviewer approached this text as a student with a physics background and an interest in glimpsing the inner sanctum of chip design and came away impressed with its clarity, depth, and no-nonsense approach. This is not a book for the fainthearted neophyte, but a challenging and rewarding introduction to HDL chip design, and a treasury as a reference book to the practicing professional. -- From Independent Publisher

| Verilog HDL, 2nd Edition: A Guide to Digital Design and Synthesis | Samir Palnitkar DecriptionA complete Verilog HDL reference which progresses from the basic Verilog concepts to the most advanced concepts in digital design, from gate, RTL and behavioural modelling to timing simulation, switch level modelling, PLI and logic synthesis. Editorial ReviewsWritten forboth experienced and new users, this book gives you broad coverage of VerilogHDL. The book stresses the practical design and verification perspective ofVerilog rather than emphasizing only the language aspects. The informationpresented is fully compliant with the IEEE 1364-2001 Verilog HDL standard. Among its many features, this edition–

Includes over 300 illustrations, examples, and exercises, and a Verilog resource list. Learning objectives and summaries are provided for each chapter.

| ||||||||||||||||||||||

| Related Courses A list of similar related courses provided by our Department. |