ΕΡΓΑΣΤΗΡΙΟ ΨΗΦΙΑΚΩΝ ΣΥΣΤΗΜΑΤΩΝ (2025-2026) (ΕCE333)

ΓΑΡΥΦΑΛΛΟΥ ΔΗΜΗΤΡΙΟΣ

Οι στόχοι του μαθήματος ECE333, "Εργαστήριο Ψηφιακών Συστημάτων", είναι

- η εκμάθηση των θεωρητικών θεμελιωδών γνώσεων σχεδίασης Ψηφιακών Συστημάτων,

- η παρουσίαση των σχετικών πρακτικών μεθοδολογιών σχεδίασης και υλοποίησης, με έμφαση στην προγραμματίσιμη λογική, και συγκεκριμένα στις FPGAs (Field Programmable Gate Array = Προγραμματίσιμος Πίνακας Πυλών στο Πεδίο), και την γλώσσα περιγραφής υλικού Verilog, και

- ο συνδυασμός θεωρίας και πράξης μέσω της πρακτικής εξοικείωσης με την υλοποίηση και δοκιμή ψηφιακών κυκλώματων στο εργαστήριο, όπου χρησιμοποιούνται πρότυπες πλακέτες ανάπτυξης υλικού με FPGAs τελευταίας τεχνολογίας.

Οι στόχοι του μαθήματος ECE333, "Εργαστήριο Ψηφιακών Συστημάτων", είναι

- η εκμάθηση των θεωρητικών θεμελιωδών γνώσεων σχεδίασης Ψηφιακών Συστημάτων,

- η παρουσίαση των σχετικών πρακτικών μεθοδολογιών σχεδίασης και υλοποίησης, με έμφαση στην προγραμματίσιμη λογική, και συγκεκριμένα στις FPGAs (Field Programmable Gate Array = Προγραμματίσιμος Πίνακας Πυλών στο Πεδίο), και την γλώσσα περιγραφής υλικού Verilog, και

- ο συνδυασμός θεωρίας και πράξης μέσω της πρακτικής εξοικείωσης με την υλοποίηση και δοκιμή ψηφιακών κυκλώματων στο εργαστήριο, όπου χρησιμοποιούνται πρότυπες πλακέτες ανάπτυξης υλικού με FPGAs τελευταίας τεχνολογίας.

Οι στόχοι του μαθήματος ECE333, "Εργαστήριο Ψηφιακών Συστημάτων", είναι

- η εκμάθηση των θεωρητικών θεμελιωδών γνώσεων σχεδίασης Ψηφιακών Συστημάτων,

- η παρουσίαση των σχετικών πρακτικών μεθοδολογιών σχεδίασης και υλοποίησης, με έμφαση στην προγραμματίσιμη λογική, και συγκεκριμένα στις FPGAs (Field Programmable Gate Array = Προγραμματίσιμος Πίνακας Πυλών στο Πεδίο), και την γλώσσα περιγραφής υλικού Verilog, και

- ο συνδυασμός θεωρίας και πράξης μέσω της πρακτικής εξοικείωσης με την υλοποίηση και δοκιμή ψηφιακών κυκλώματων στο εργαστήριο, όπου χρησιμοποιούνται πρότυπες πλακέτες ανάπτυξης υλικού με FPGAs τελευταίας τεχνολογίας.

Περίγραμμα

Ώρες Διδασκαλίας

Διαλέξεις

Εργαστήριο

Διαθέσιμες Ώρες Πλακέτας

(Θα ανακοινωθούν)

ΔΕΥΤΕΡΑ

ΤΡΙΤΗ

ΤΕΤΑΡΤΗ

ΠΕΜΠΤΗ

ΠΑΡΑΣΚΕΥΗ

09.00 - 11.00

Αίθουσα

305

11.00 - 13.00

Αίθουσα

305

18.00 - 20.00

Εργαστήριο 206

[1ο Τμήμα]

20.00 - 22.00

Εργαστήριο 206

[2ο Τμήμα]

Προτεινόμενα συγγράμματα

- Ψηφιακή Σχεδίαση, 6η Έκδοση: Με Εκτενή Παρουσίαση των Verilog, VHDL και SystemVerilog

- Author(s): Morris Mano, Michael Ciletti | Κωδικός Βιβλίου στον Εύδοξο: 68406394 - ISBN: 978-960-491-113-4

- Ψηφιακή Σχεδίαση, 3η Έκδοση: Αρχές και Πρακτικές

- Authos(s): John F. Wakerly | Κωδικός Βιβλίου στον Εύδοξο: 13946 - ISBN: 960-209-728-0

- HDL Chip Design: A Practical Guide for Designing, Synthesizing & Simulating ASICs & FPGAs Using VHDL or Verilog

- Author(s): Douglas J. Smith | Κωδικός Βιβλίου στον Εύδοξο: x - ISBN: 978-0965193436

- Verilog HDL, 2nd Edition: A Guide to Digital Design and Synthesis

- Author(s): Samir Palnitkar | Κωδικός Βιβλίου στον Εύδοξο: x - ISBN: 978-0132599702

For more details see e-Class "Links" -> "Related Course Books"

Μαθησιακοί Στόχοι

Επανάληψη Βασικών Εννοιών Ψηφιακής Σχεδίασης

- Δυαδικοί Αριθμοί, Ψηφιακή Λογική και Ηλεκτρικά Χαρακτηριστικά Κυκλώματος

- Δυαδική Άλγεβρα και Δυαδικές Συναρτήσεις

- Συνδυαστικές και Ακολουθιακές Πύλες (Flip-Flop και Latch)

- Συνθήκες Ορθής Λειτουργίας

- Μηχανές Πεπερασμένων Καταστάσεων (ΜΠΚ)

- Είδη Κυκλωμάτων

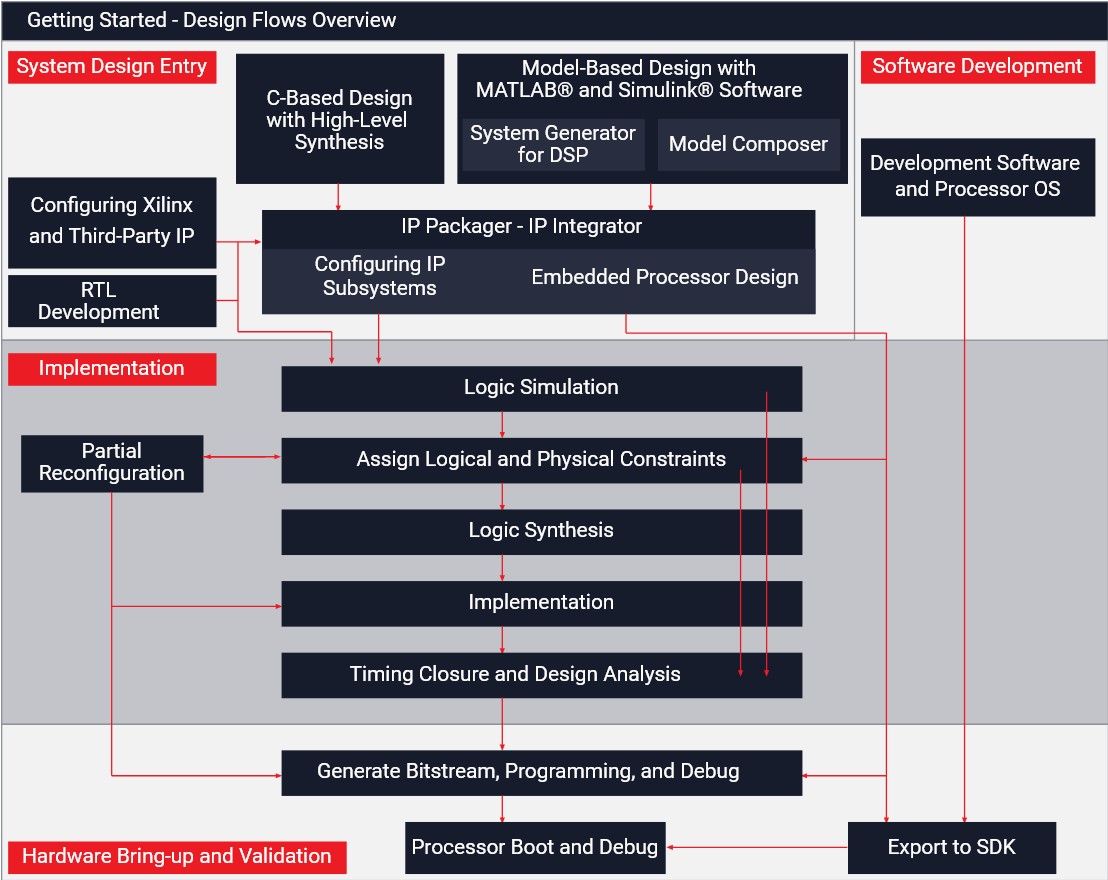

Τυπική Ροή Ηλεκτρονικού Σχεδιαστικού Αυτοματισμού

- Βασικά Στάδια Ροής Ηλεκτρονικού Σχεδιαστικού Αυτοματισμού

- Ιεραρχική Σχεδίαση

- Επίπεδα Αφαίρεσης στη Σχεδίαση - Γλώσσες Περιγραφής Υλικού

H Γλώσσα Περιγραφής Υλικού Verilog

- Δυνατότητες της Γλώσσας, Αναπαράσταση και Υλοποίηση σε Verilog

- Μονάδες, Εμφανίσεις, Συντακτική Δομή, Χρόνος στην Verilog

- Θεμελιώδη Στοιχεία, Τύποι Μοντελοποίησης, Συμβάσεις της Γλώσσας

- Αναπαράσταση Αριθμών, Τελεστές, Τύποι Μεταβλητών

- Αναθέσεις, Θύρες και Συνδέσεις, Δίαυλοι (Busses)

- Συνθήκες if/else, case, Συνθεσιμότητα, Λειτουργικός Έλεγχος

- Λίστες Ευαισθησίας, Τμήματα initial/always, Συνένωση Σημάτων

- Βρόχοι for/while, Παράμετροι, Μνήμες, Συναρτήσεις, Διαδικασίες

- Γεγονότα, Καθυστερήσεις, Εξαρτήσεις Παράλληλων Τμημάτων

- Συνθέσιμες Δομές και Κυκλωματική Απεικόνιση

- Flip-Flops, Μετρητές, Συσσωρευτές, Ολισθητές, Πολυπλέκτες

- Κωδικοποιητές, Απο-Κωδικοποιητές, Αθροιστές, Συγκριτές

- Ανιχνευτής Ακμής, D-Latch, Σύγχρονη/Ασύγχρονη Μνήμη

- Περιγραφή ΜΠΚ σε Verilog

Αριθμητικά Κυκλώματα

- Ημι- και Πλήρης Αθροιστής, Αθροιστής Σειριακού Κρατουμένου

- Αθροιστής Πρόγνωσης Κρατουμένου, Παραγωγή και Προώθηση Κρατουμένου

- Αλγόριθμος Πολλαπλασιασμού, Πολλαπλασιαστής Ολίσθησης-Πρόσθεσης

- Πολλαπλασιαστής με Πίνακα Αποτελεσμάτων, Πολλαπλασιαστής μερικών Παραγόντων

- Αλγόριθμος Διαίρεσης, Σύγκριση, Ολίσθηση και Αφαίρεση

Συγχρονισμός και Μεταστάθεια

- Περιπτώσεις Συγχρονισμού, Καμπύλη Μεταβίβασης και Μηχανικό Ανάλογο

- Συγχρονισμός με Flip-Flop, Μεταστάθεια, Συγχρονιστής δυο Flip-Flop

- Πιθανότητα Μεταστάθειας, Μέσος Χρόνος μεταξύ Αποτυχιών

- Συγχρονισμός με Πρωτόκολλο Χειραψίας και Ουρά

Μηχανές Πεπερασμένων Καταστάσεων (ΜΠΚ)

- Ορισμός ΜΠΚ, Πίνακας Ροής, Γράφος Καταστάσεων

- Μηχανές Mealy/Moore, Κωδικοποίηση, Υλοποίηση ΜΠΚ σε Δυαδική Λογική

- Αρχικοποίηση, Ντετερμινισμός, Αδιάφορες Τιμές

- Διαδραστικές ΜΠΚ, Σύνθεση Πολλαπλών ΜΠΚ

- Ισοδύναμες Καταστάσεις, Κ-διάκριση, Κ-ισοδυναμία

- Ελαχιστοποίηση Πλήρως-Ορισμένων ΜΠΚ, Ελαχιστοποίηση με Αδιάφορες Τιμές

Δυαδική Άλγεβρα, Δυαδική Βελτιστοποίηση

- Απεικόνιση Συναρτήσεων στον Πολυδιάστατο Δυαδικό Χώρο

- Θεώρημα Boole/Shannon, Κανονικές Μορφές, Ελαχιστόροι/Μεγιστόροι

- Ομοφωνία, Συνεπαγωγή, Πρόβλημα SAT, Αδιάφορες Τιμές SDC/ODC

- Ταυτολογία, Επάγοντες και Πρώτοι Επάγοντες Όροι

- Ουσιώδης Επάγοντες, Θεώρημα Quine/McCluskey

- Υπολογισμός Πρώτων με τη μέθοδο Πίνακα, Μονόσημο Πρόβλημα Κάλυψης

- Αδιάφορες Τιμές, Συναρτήσεις Πολλαπλών Εξόδων

Χρονισμός, Στατική Χρονική Ανάλυση

- Καθυστέρηση Συνδυαστικής, Ακολουθιακής Πύλης, Περιορισμοί Πρό-θεσης/Διατήρησης

- Μοντέλο Σύγχρονου Κυκλώματος - Είδη Μονοπατιών, Στατική Ανάλυση

- Ελάχιστη Περίοδος, Παραβιάσεις Διατήρησης, Σχεδίαση Δέντρων Ρολογιών

- Φραγή Ρολογιού

Εργαστήριο

Το ECE-333 έχει πρακτικό χαρακτήρα με έμφαση στην ενασχόληση στο πεδίο. Το μάθημα απαιτεί εξάσκηση, εξοικείωση και απασχόληση στο εργαστήριο ώστε να επιτευχθούν οι παρακάτω στόχοι:

- η εξοικείωση με τις πρότυπες πλακέτες FPGA.

- ο προγραμματισμός των πλακετών για την περάτωση των Εργαστηριακών Εργασιών, και η δοκιμή της ορθής τους λειτουργίας, και

- η συζήτηση θεωρητικών και πρακτικών ερωτήσεων του μαθήματος, καθώς και πρακτικών προβλημάτων στην υλοποίηση των Εργασιών με τον διδάσκοντα και τους βοηθούς.

Το εργαστήριο θα εποπτεύεται από τον Διδάσκοντα και τους Βοηθούς, με στόχο να βοηθήσουν στην εξοικείωση με το υλικό και στην επίλυση προβλημάτων. Όμως, είναι ουσιαστική και χρήσιμη η καλή προετοιμασία, λ.χ. η υλοποίηση μέρος ή όλου του κυκλώματος της σχετικής Εργασίας από πριν, και η δοκιμή του μέσω προσομοίωσης.

Τα εργαστήρια του μαθήματος γίνονται στο Εργαστήριο Ηλεκτρονικής 206, και οι εγγεγραμμένοι φοιτητές θα πρέπει να επιλέξουν εργαστηριακή ομάδα και ώρα σε συνεννόηση με τον διδάσκοντα ή τους βοηθούς.

Μέθοδοι αξιολόγησης

- Εργαστήρια: 60% Βαθμού

- Πρόοδος: 15% Βαθμού

- Τελική Εξέταση: 25% Βαθμού

Προαπαιτούμενα Μαθήματα

Το ECE-333 ΔΕΝ έχει προαπαιτούμενα μαθήματα.

Συνιστώμενα Μαθήματα

Το ECE-333 έχει ως συνιστώμενα μαθήματα τα:

Περισσότερα

Το μάθημα είναι επιλογής 5ου εξαμήνου (Ε4), αντιστοιχεί σε 4 Διδακτικές Μονάδες, 6 μονάδες ECTS και βρίσκεται στην Περιοχή του Υλικού και Αρχιτεκτονικής Υπολογιστών (ΥΑ).

Διαλέξεις |

Εργαστήριο |

|

Διαθέσιμες Ώρες Πλακέτας

(Θα ανακοινωθούν) |

||

ΔΕΥΤΕΡΑ |

ΤΡΙΤΗ |

ΤΕΤΑΡΤΗ |

ΠΕΜΠΤΗ |

ΠΑΡΑΣΚΕΥΗ |

|

| 09.00 - 11.00 |

Αίθουσα |

|

|||

| 11.00 - 13.00 |

|

Αίθουσα |

|||

| 18.00 - 20.00 |

Εργαστήριο 206 |

||||

| 20.00 - 22.00 |

Εργαστήριο 206 |

||||

- Ψηφιακή Σχεδίαση, 6η Έκδοση: Με Εκτενή Παρουσίαση των Verilog, VHDL και SystemVerilog

- Author(s): Morris Mano, Michael Ciletti | Κωδικός Βιβλίου στον Εύδοξο: 68406394 - ISBN: 978-960-491-113-4

- Author(s): Morris Mano, Michael Ciletti | Κωδικός Βιβλίου στον Εύδοξο: 68406394 - ISBN: 978-960-491-113-4

- Ψηφιακή Σχεδίαση, 3η Έκδοση: Αρχές και Πρακτικές

- Authos(s): John F. Wakerly | Κωδικός Βιβλίου στον Εύδοξο: 13946 - ISBN: 960-209-728-0

- HDL Chip Design: A Practical Guide for Designing, Synthesizing & Simulating ASICs & FPGAs Using VHDL or Verilog

- Author(s): Douglas J. Smith | Κωδικός Βιβλίου στον Εύδοξο: x - ISBN: 978-0965193436

- Verilog HDL, 2nd Edition: A Guide to Digital Design and Synthesis

- Author(s): Samir Palnitkar | Κωδικός Βιβλίου στον Εύδοξο: x - ISBN: 978-0132599702

For more details see e-Class "Links" -> "Related Course Books"

Επανάληψη Βασικών Εννοιών Ψηφιακής Σχεδίασης

- Δυαδικοί Αριθμοί, Ψηφιακή Λογική και Ηλεκτρικά Χαρακτηριστικά Κυκλώματος

- Δυαδική Άλγεβρα και Δυαδικές Συναρτήσεις

- Συνδυαστικές και Ακολουθιακές Πύλες (Flip-Flop και Latch)

- Συνθήκες Ορθής Λειτουργίας

- Μηχανές Πεπερασμένων Καταστάσεων (ΜΠΚ)

- Είδη Κυκλωμάτων

Τυπική Ροή Ηλεκτρονικού Σχεδιαστικού Αυτοματισμού

- Βασικά Στάδια Ροής Ηλεκτρονικού Σχεδιαστικού Αυτοματισμού

- Ιεραρχική Σχεδίαση

- Επίπεδα Αφαίρεσης στη Σχεδίαση - Γλώσσες Περιγραφής Υλικού

H Γλώσσα Περιγραφής Υλικού Verilog

- Δυνατότητες της Γλώσσας, Αναπαράσταση και Υλοποίηση σε Verilog

- Μονάδες, Εμφανίσεις, Συντακτική Δομή, Χρόνος στην Verilog

- Θεμελιώδη Στοιχεία, Τύποι Μοντελοποίησης, Συμβάσεις της Γλώσσας

- Αναπαράσταση Αριθμών, Τελεστές, Τύποι Μεταβλητών

- Αναθέσεις, Θύρες και Συνδέσεις, Δίαυλοι (Busses)

- Συνθήκες if/else, case, Συνθεσιμότητα, Λειτουργικός Έλεγχος

- Λίστες Ευαισθησίας, Τμήματα initial/always, Συνένωση Σημάτων

- Βρόχοι for/while, Παράμετροι, Μνήμες, Συναρτήσεις, Διαδικασίες

- Γεγονότα, Καθυστερήσεις, Εξαρτήσεις Παράλληλων Τμημάτων

- Συνθέσιμες Δομές και Κυκλωματική Απεικόνιση

- Flip-Flops, Μετρητές, Συσσωρευτές, Ολισθητές, Πολυπλέκτες

- Κωδικοποιητές, Απο-Κωδικοποιητές, Αθροιστές, Συγκριτές

- Ανιχνευτής Ακμής, D-Latch, Σύγχρονη/Ασύγχρονη Μνήμη

- Περιγραφή ΜΠΚ σε Verilog

Αριθμητικά Κυκλώματα

- Ημι- και Πλήρης Αθροιστής, Αθροιστής Σειριακού Κρατουμένου

- Αθροιστής Πρόγνωσης Κρατουμένου, Παραγωγή και Προώθηση Κρατουμένου

- Αλγόριθμος Πολλαπλασιασμού, Πολλαπλασιαστής Ολίσθησης-Πρόσθεσης

- Πολλαπλασιαστής με Πίνακα Αποτελεσμάτων, Πολλαπλασιαστής μερικών Παραγόντων

- Αλγόριθμος Διαίρεσης, Σύγκριση, Ολίσθηση και Αφαίρεση

Συγχρονισμός και Μεταστάθεια

- Περιπτώσεις Συγχρονισμού, Καμπύλη Μεταβίβασης και Μηχανικό Ανάλογο

- Συγχρονισμός με Flip-Flop, Μεταστάθεια, Συγχρονιστής δυο Flip-Flop

- Πιθανότητα Μεταστάθειας, Μέσος Χρόνος μεταξύ Αποτυχιών

- Συγχρονισμός με Πρωτόκολλο Χειραψίας και Ουρά

Μηχανές Πεπερασμένων Καταστάσεων (ΜΠΚ)

- Ορισμός ΜΠΚ, Πίνακας Ροής, Γράφος Καταστάσεων

- Μηχανές Mealy/Moore, Κωδικοποίηση, Υλοποίηση ΜΠΚ σε Δυαδική Λογική

- Αρχικοποίηση, Ντετερμινισμός, Αδιάφορες Τιμές

- Διαδραστικές ΜΠΚ, Σύνθεση Πολλαπλών ΜΠΚ

- Ισοδύναμες Καταστάσεις, Κ-διάκριση, Κ-ισοδυναμία

- Ελαχιστοποίηση Πλήρως-Ορισμένων ΜΠΚ, Ελαχιστοποίηση με Αδιάφορες Τιμές

Δυαδική Άλγεβρα, Δυαδική Βελτιστοποίηση

- Απεικόνιση Συναρτήσεων στον Πολυδιάστατο Δυαδικό Χώρο

- Θεώρημα Boole/Shannon, Κανονικές Μορφές, Ελαχιστόροι/Μεγιστόροι

- Ομοφωνία, Συνεπαγωγή, Πρόβλημα SAT, Αδιάφορες Τιμές SDC/ODC

- Ταυτολογία, Επάγοντες και Πρώτοι Επάγοντες Όροι

- Ουσιώδης Επάγοντες, Θεώρημα Quine/McCluskey

- Υπολογισμός Πρώτων με τη μέθοδο Πίνακα, Μονόσημο Πρόβλημα Κάλυψης

- Αδιάφορες Τιμές, Συναρτήσεις Πολλαπλών Εξόδων

Χρονισμός, Στατική Χρονική Ανάλυση

- Καθυστέρηση Συνδυαστικής, Ακολουθιακής Πύλης, Περιορισμοί Πρό-θεσης/Διατήρησης

- Μοντέλο Σύγχρονου Κυκλώματος - Είδη Μονοπατιών, Στατική Ανάλυση

- Ελάχιστη Περίοδος, Παραβιάσεις Διατήρησης, Σχεδίαση Δέντρων Ρολογιών

- Φραγή Ρολογιού

Το ECE-333 έχει πρακτικό χαρακτήρα με έμφαση στην ενασχόληση στο πεδίο. Το μάθημα απαιτεί εξάσκηση, εξοικείωση και απασχόληση στο εργαστήριο ώστε να επιτευχθούν οι παρακάτω στόχοι:

- η εξοικείωση με τις πρότυπες πλακέτες FPGA.

- ο προγραμματισμός των πλακετών για την περάτωση των Εργαστηριακών Εργασιών, και η δοκιμή της ορθής τους λειτουργίας, και

- η συζήτηση θεωρητικών και πρακτικών ερωτήσεων του μαθήματος, καθώς και πρακτικών προβλημάτων στην υλοποίηση των Εργασιών με τον διδάσκοντα και τους βοηθούς.

Το εργαστήριο θα εποπτεύεται από τον Διδάσκοντα και τους Βοηθούς, με στόχο να βοηθήσουν στην εξοικείωση με το υλικό και στην επίλυση προβλημάτων. Όμως, είναι ουσιαστική και χρήσιμη η καλή προετοιμασία, λ.χ. η υλοποίηση μέρος ή όλου του κυκλώματος της σχετικής Εργασίας από πριν, και η δοκιμή του μέσω προσομοίωσης.

Τα εργαστήρια του μαθήματος γίνονται στο Εργαστήριο Ηλεκτρονικής 206, και οι εγγεγραμμένοι φοιτητές θα πρέπει να επιλέξουν εργαστηριακή ομάδα και ώρα σε συνεννόηση με τον διδάσκοντα ή τους βοηθούς.

- Εργαστήρια: 60% Βαθμού

- Πρόοδος: 15% Βαθμού

- Τελική Εξέταση: 25% Βαθμού

Το ECE-333 ΔΕΝ έχει προαπαιτούμενα μαθήματα.

Το ECE-333 έχει ως συνιστώμενα μαθήματα τα:

Το μάθημα είναι επιλογής 5ου εξαμήνου (Ε4), αντιστοιχεί σε 4 Διδακτικές Μονάδες, 6 μονάδες ECTS και βρίσκεται στην Περιοχή του Υλικού και Αρχιτεκτονικής Υπολογιστών (ΥΑ).