#### ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ & ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

# ΕCE119 – Ψηφιακή Σχεδίαση

Διδάσκοντες Εργαστηρίου: Δ. Καραμπερόπουλος

Α. Φεύγας

Lab 6: Encoders and Decoders

## Περιεχόμενα Εργαστηριακού Μαθήματος

- Εισαγωγή

- Lab 1: Multisim Circuit Simulation and Basic Gates

- Lab 2: Truth Tables and Basic Logic Gates

- Lab 3: Logic Gates Explored and Boolean Algebra

- Lab 4: Karnaugh Maps

- Lab 5: Binary Conversion and Adders

- Lab 6: Encoders and Decoders

- Lab 7: Multiplexers and Demultiplexers

- Lab 8: Latches and Sequential Logic Circuits

- Lab 9: Flip-Flops

- Lab 10: Sequential Circuits FSM (1°)

- Lab 11: Sequential Circuits FSM (2°)

#### **Encoders and Decoders**

- In Lab 5, we learned that gates arranged to perform a specific function, such as binary addition, can be represented with a chip.

- Other applications of this concept include encoders and decoders.

- Encoders are logic circuits responsible for reducing the size of an input.

- Decoders preform the inverse operation, increasing the size of an input.

- In a previous lab, we learned what a seven-segment display is and in this lab we will explore how decoders apply to this electronic device.

## **Learning Objectives**

#### In this lab, students will:

- Explain how decoders works, specifically in an SSD

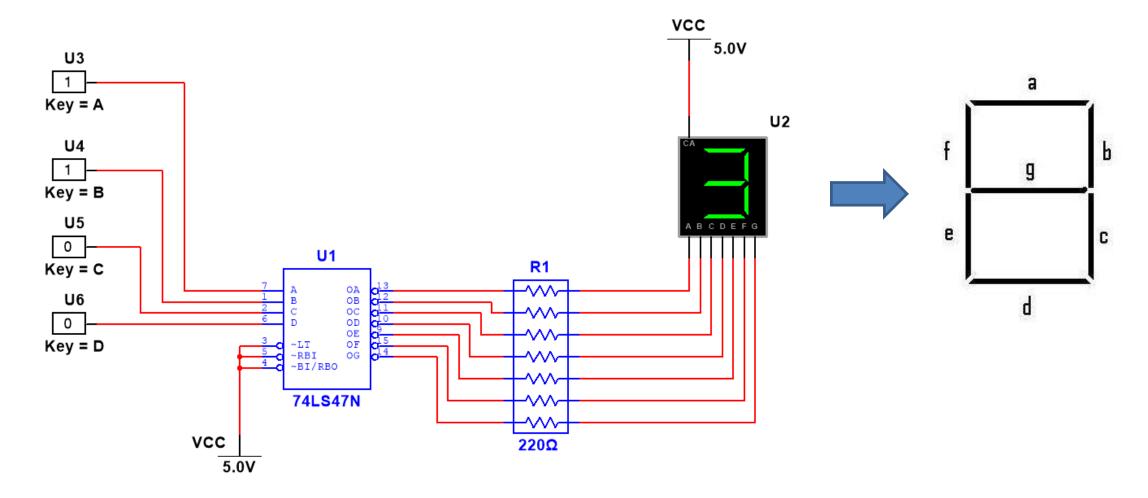

- Create a circuit with a BCD to Seven Segment Display Decoder and verify its truth table

In this lab, you will collect the following deliverables:

- Diagram of a BCD to 7 Segment Display Decoder

- Truth tables

- Conclusion questions

The process of translating ambiguous information into something understood by a device receiving the data is called **decoding**.

Therefore, the resulting device is known as a **decoder**.

#### **Decoders**

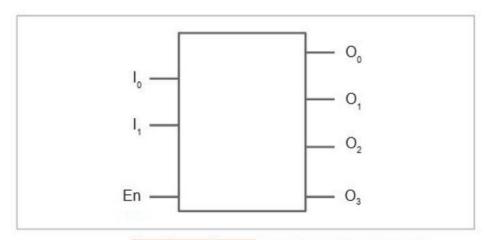

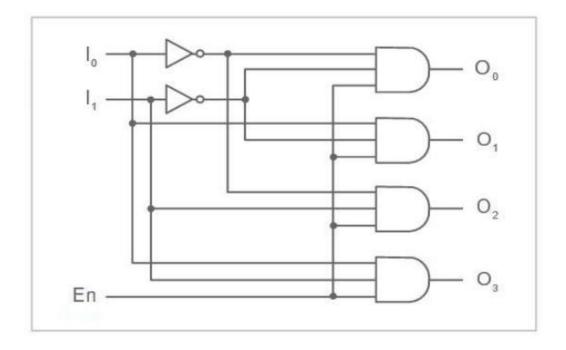

Let's take the example of a 2 to 4 decoder enabled when the En signal is 1 (active-high):

| En | $I_{i}$ | l <sub>o</sub> | O <sub>3</sub> | 0, | 0, | O <sub>0</sub> |

|----|---------|----------------|----------------|----|----|----------------|

| 1  | 0       | 0              | 0              | 0  | 0  | 1              |

| 1  | 0       | 1              | 0              | 0  | 1  | 0              |

| 1  | 1       | 0              | 0              | 1  | 0  | 0              |

| 1  | 1       | 1              | 1              | 0  | 0  | 0              |

| 0  | X       | X              | 0              | 0  | 0  | 0              |

#### **Decoders**

- Decoders take binary codes of n bits and generate 2<sup>n</sup> outputs.

- The outputs of a binary decoder are said to be **one-hot encoded** because for any combination of the input signals there is only one output having the value 1.

- Decoders can include an enable signal for controlling the circuit operation.

- This enable signal can be active-low (meaning that the circuit will operate only when enable is 0) or active-high (the decoder is enabled when enable is 1).

- Decoders with enable inputs can be used for constructing larger decoders.

- One of the most important applications of decoders is <u>memory access</u>, where they are used for decoding the address of the rows in the memory blocks.

### **Decoders - 2x4 line decoder with enable input**

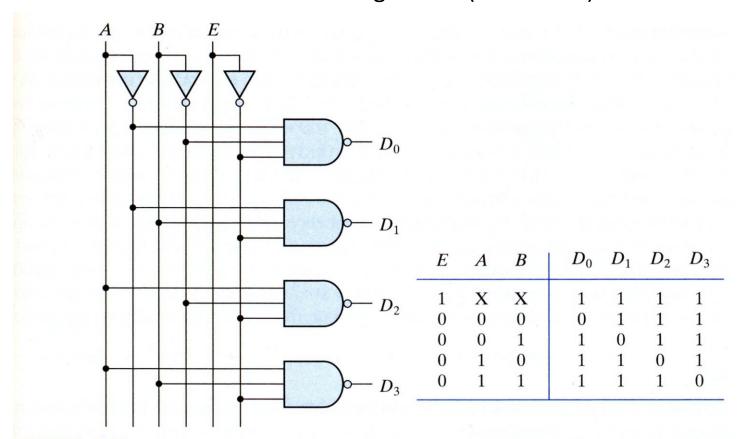

And a 2 to 4 decoder enabled when the En signal is 0 (active-low):

**ΣΧΗΜΑ 4.19**

Αποκωδικοποιητής 2 × 4 με είσοδο επίτρεψης

#### **Encoders**

**Encoders** are logic circuits that perform the opposite function of a decoder.

Binary encoders encode information from 2<sup>n</sup> input lines, producing an n-bit code.

#### **Encoders**

- At any given time, only one of the 2<sup>n</sup> inputs can be 1.

- Encoding is used for <u>reducing the number of bits</u> needed to represent information. They are often used in application such as data transmission and data storing.

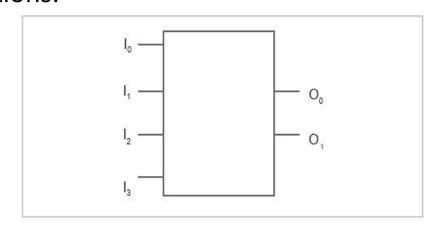

- The graphical symbol of the 4 to 2 binary encoder is presented below. The cases in which more than one input is 1 are not shown in the truth table because they are treated as don't care conditions.

| I <sub>3</sub> | l <sub>2</sub> | I, | I <sub>o</sub> | 0, | O <sub>0</sub> |

|----------------|----------------|----|----------------|----|----------------|

| 0              | 0              | 0  | 1              | 0  | 0              |

| 0              | 0              |    | 0              | 0  | 1              |

| 0              | 1              |    | 0              | 1  | 0              |

| 1              | 0              | 0  | 0              | 1  | 1              |

#### **Encoders**

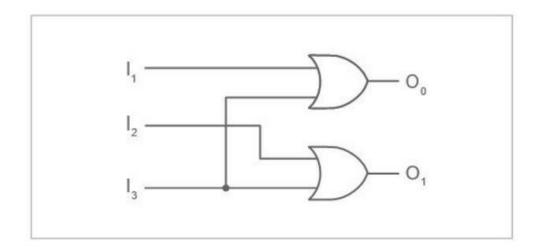

- It can be seen in the truth table that the output  $O_1$  is 1 when either  $I_3$  or  $I_2$  is 1 and that the output  $O_0$  is 1 when either  $I_3$  or  $I_1$  is 1.

- It can also be seen that the input Io can be ignored

- The encoders presented so far are considered to have one-hot encoded inputs.

| I <sub>3</sub> | I <sub>2</sub> | I, | I <sub>o</sub> | 0, | O <sub>0</sub> |

|----------------|----------------|----|----------------|----|----------------|

| 0              | 0              | 0  | 1              | 0  | 0              |

| 0              |                |    | 0              | 0  | 1              |

| 0              |                | 1  | 0              | 1  | 0              |

| 1              | 0              | 0  | 0              | 1  | 1              |

## **Priority encoders**

- Priority encoders are able to prioritize inputs

- This is important because regular encoders can generate the wrong output when there is more than one input present at logic level 1.

- This type of encoder has an additional output, z, which indicates the case in which none of the inputs is 1.

## **Priority encoders**

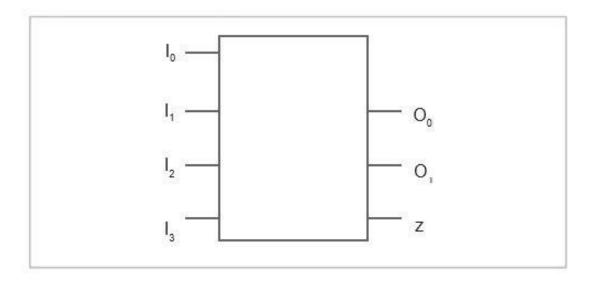

- The graphical symbol of the priority encoder is presented below.

- The truth table describes the behavior of a 4-to-2 priority encoder.

- It can be seen on the last line of the truth table that if the input I<sub>3</sub> is 1, the outputs are all 1 and the values on the other inputs of the decode do not matter and are denoted by 'x'.

| $I_3$ | l <sub>2</sub> | I, | l <sub>o</sub> | 0, | O <sub>0</sub> | z |

|-------|----------------|----|----------------|----|----------------|---|

| 0     | 0              | 0  | 0              | х  | X              | 0 |

| 0     | 0              | 0  | 1              | 0  | 0              | 1 |

| 0     | 0              | 1  | X              | 0  | 1              | 1 |

| 0     | 1              | x  | x              | 1  | 0              | 1 |

| 1     | X              |    |                | 1  | 1              | 1 |

## **BCD to Seven Segment Display Decoder**

## Ευχαριστώ για την προσοχή σας!

> Ερωτήσεις / Απορίες ;

Επικοινωνία: ece119.uth@gmail.com