#### ΤΜΗΜΑ ΗΛΕΚΤΡΟΛΟΓΩΝ ΜΗΧΑΝΙΚΩΝ & ΜΗΧΑΝΙΚΩΝ ΥΠΟΛΟΓΙΣΤΩΝ

# ΕCE119 – Ψηφιακή Σχεδίαση

Διδάσκοντες Εργαστηρίου: Δ. Καραμπερόπουλος

Α. Φεύγας

Δ. Γαρυφάλλου

Lab 7: Multiplexers and Demultiplexers

## Περιεχόμενα Εργαστηριακού Μαθήματος

- Εισαγωγή

- Lab 1: Multisim Circuit Simulation and Basic Gates

- Lab 2: Truth Tables and Basic Logic Gates

- Lab 3: Logic Gates Explored and Boolean Algebra

- Lab 4: Karnaugh Maps

- Lab 5: Binary Conversion and Adders

- Lab 6: Encoders and Decoders

- Lab 7: Multiplexers and Demultiplexers

- Lab 8: Latches and Sequential Logic Circuits

- Lab 9: Flip-Flops

- Lab 10: Sequential Circuits FSM

#### **Multiplexers and Demultiplexers**

- Multiplexers are combinational logic circuits for which there are multiple potential inputs but there is always only one output.

- Demultiplexers are the opposite in that there is always one input but there are multiple potential outputs.

- Both multiplexers and demultiplexers have a bit (or multiple bits) called selector bit(s) which is responsible for determining which input or output is chosen.

- Like encoders and decoders, multiplexers and demultiplexers can be broken down into circuit components but are typically represented by chips for visual simplification.

- In this lab, we will analyze multiplexers and demultiplexers in both their circuit and chip forms.

#### **Learning Objectives**

#### In this lab, students will:

- Reflect on the similarities and differences between encoders and multiplexers

- Examine the function of a basic 2-to-1 Multiplexer using logic gates

#### **Expected Deliverables**

In this lab, you will collect the following deliverables:

- Sum-of-Products Boolean functions for 2-to-1 Multiplexer

- Sum-of-Products Boolean functions for 1-to4 Demultiplexer

- Image of circuit

- Observations of demultiplexer behavior

- Conclusion questions

#### Multiplexers (1/3)

The multiplexer, abbreviated MUX, is a combinational logic circuit which has multiple data inputs, one or more select inputs and one output.

- It passes the data on one of the inputs, depending on the selection signals, to the output

- With the help of this logic circuit, multiple signals can share the same data output

- Multiplexers have 2<sup>s</sup> inputs and s selector lines, which determine which of the inputs to output.

- Multiplexers are one of the most widely used combinational circuits, their application areas include:

- Data routing

- Operation sequencing

- Parallel-to-serial conversion

- Waveform generation

#### Multiplexers (2/3)

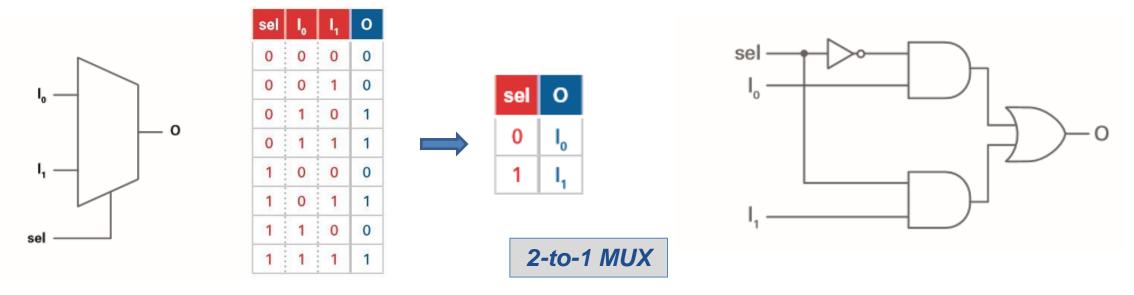

- The simplest circuit is the 2-to-1 multiplexer, with the graphical symbol presented in the leftmost figure.

- Its functionality is described by the joining truth table.

- The multiplexer below is only 1-bit wide since bit line is connected to a single output bit line.

# Multiplexers (3/3)

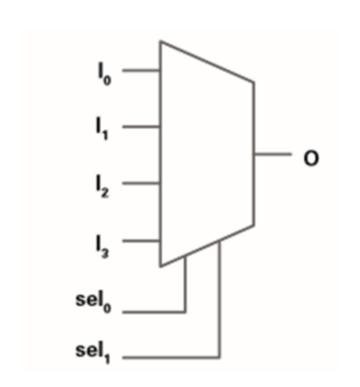

| sel, | sel <sub>o</sub> | 0              |

|------|------------------|----------------|

| 0    | 0                | I <sub>o</sub> |

| 0    | 1                | I <sub>1</sub> |

| 1    | 0                | l <sub>2</sub> |

| 1    | 1                | l <sub>3</sub> |

4-to-1 MUX

#### Demultiplexers (1/2)

#### **Demultiplexers (DEMUX)** have the opposite function of a multiplexer

- It places the value of a single data input on several data outputs depending on a selection signal

- Usually demultiplexers have s select inputs and 2s outputs

- Since demultiplexers take one input and connect it to many outputs, some of their uses are for communication (two-way communication usually includes both multiplexers and demultiplexers) and for serial to parallel converters

### **Demultiplexers (2/2)**

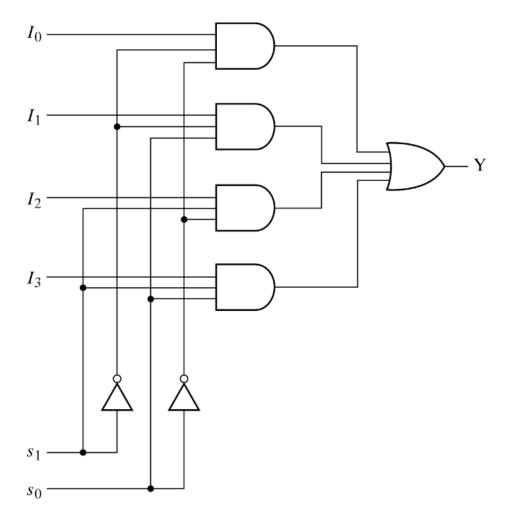

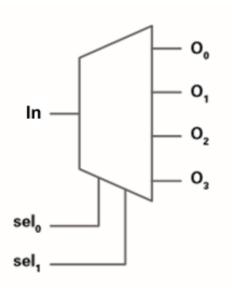

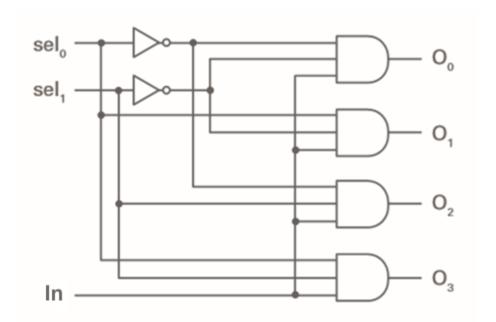

The graphical symbol for a 1-to-4 demultiplexer is shown below (left) as well as the corresponding 1-to-4 DEMUX truth table (center) and the CLC (right)

| sel, | sel <sub>o</sub> | 03 | 0, | 0, | 0, |

|------|------------------|----|----|----|----|

| 0    | 0                | 0  | 0  | 0  | ln |

| 0    | 1                | 0  | 0  | In | 0  |

| 1    | 0                | 0  | In | 0  | 0  |

| 1    | 1                | In | 0  | 0  | 0  |

1-to-4 DEMUX

### Ευχαριστώ για την προσοχή σας!

Ερωτήσεις / Απορίες ;

Επικοινωνία: ece119.uth@gmail.com