Fall Semester - 2022

I. Lilitsis, I. Gkolfos, S. Simoglou, C. Sotiriou

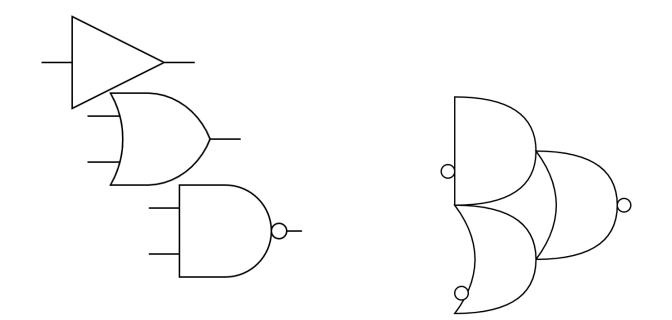

- Combinational Elements:

- Implement stateless Boolean functions

- Output is always produced upon any input change

- Combinational Elements:

- Implement stateless Boolean functions

- Output is always produced upon any input change

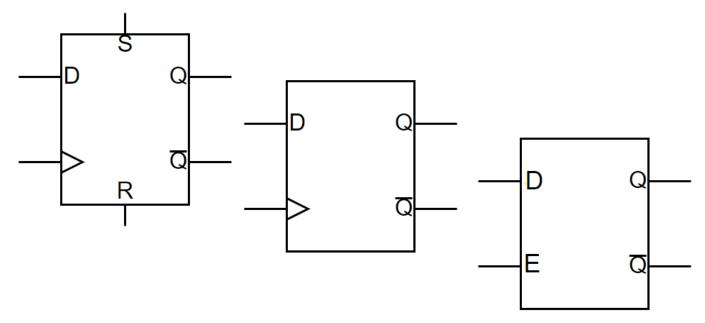

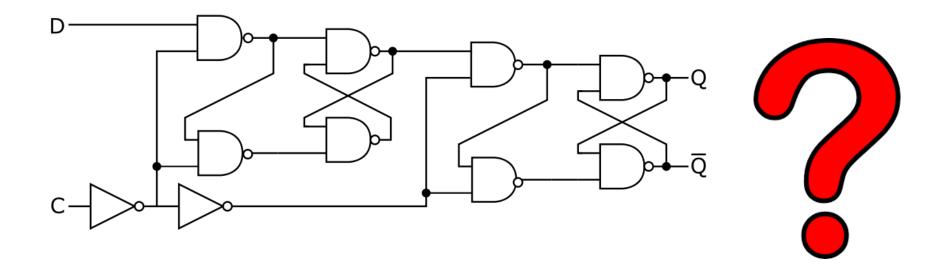

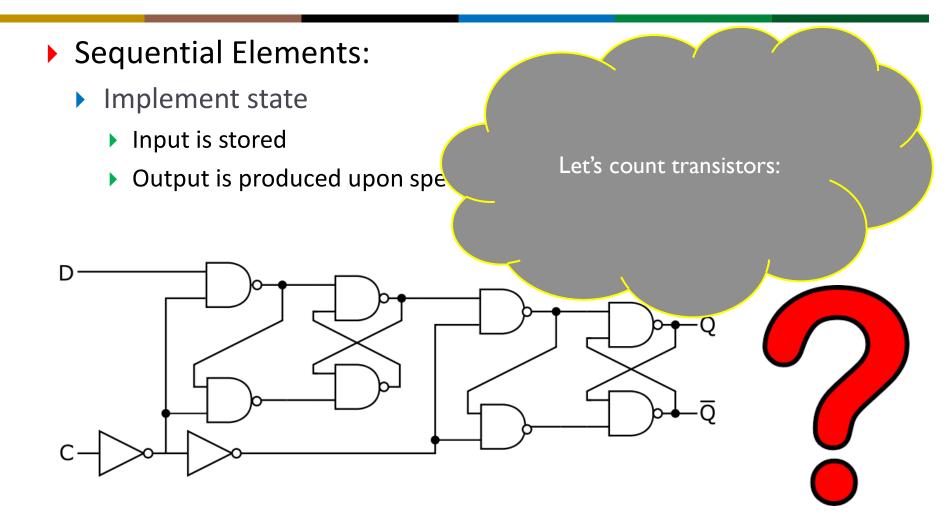

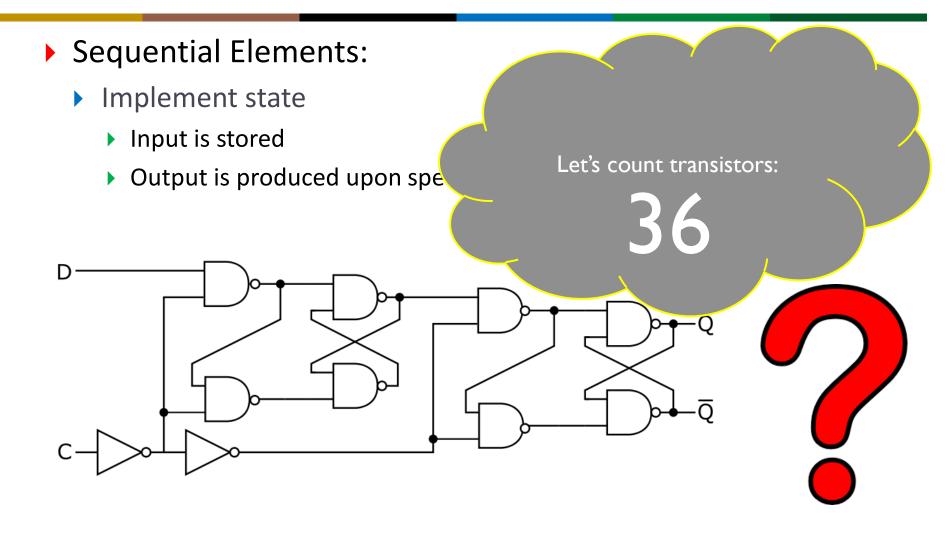

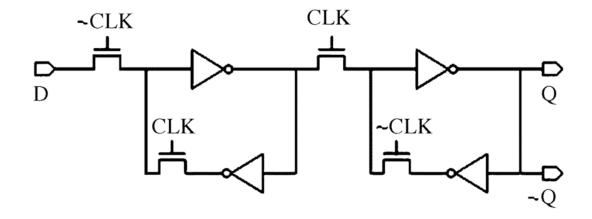

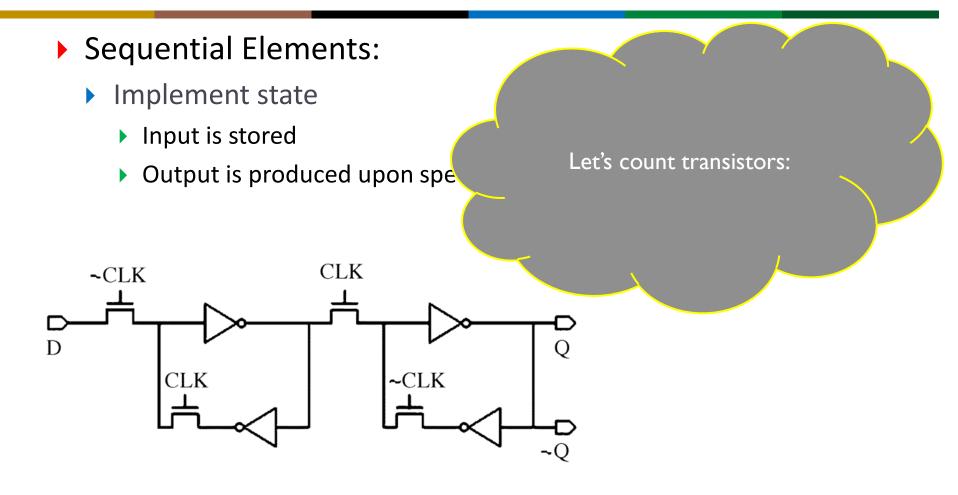

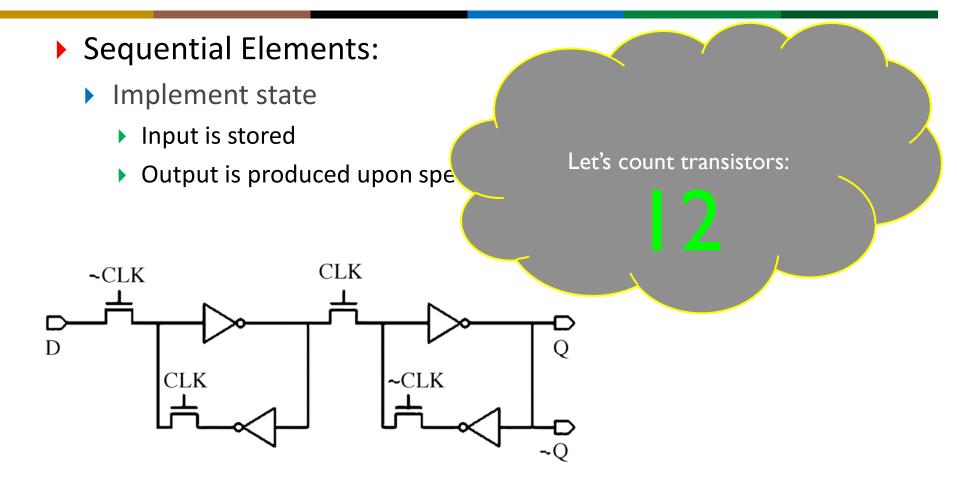

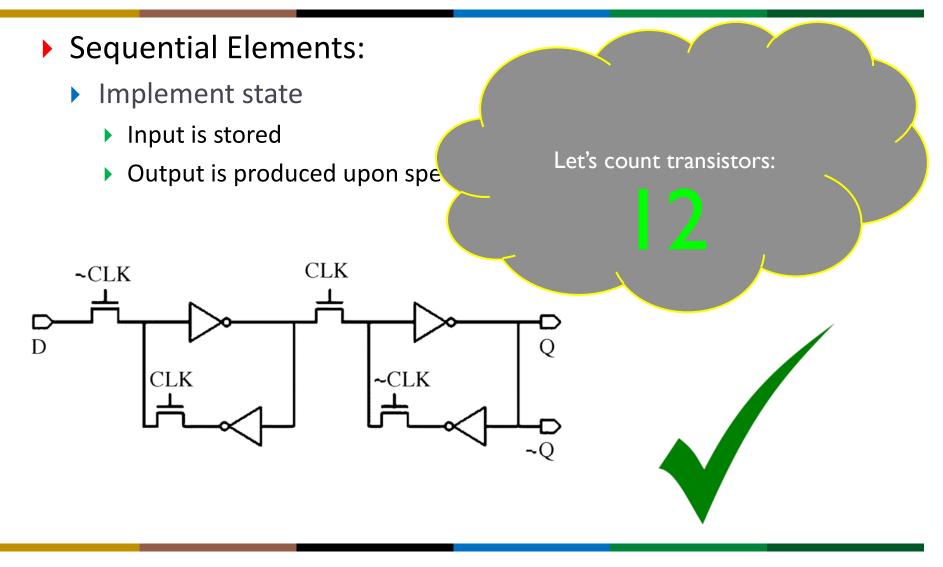

- Sequential Elements:

- Implement state

- Input is stored

- Output is produced upon specific triggering events, i.e. clock edges

- Sequential Elements:

- Implement state

- Input is stored

- Output is produced upon specific triggering events, i.e. clock edges

- Sequential Elements:

- Implement state

- Input is stored

- Output is produced upon specific triggering events, i.e. clock edges

- Complex:

- Implement both state and Boolean operations

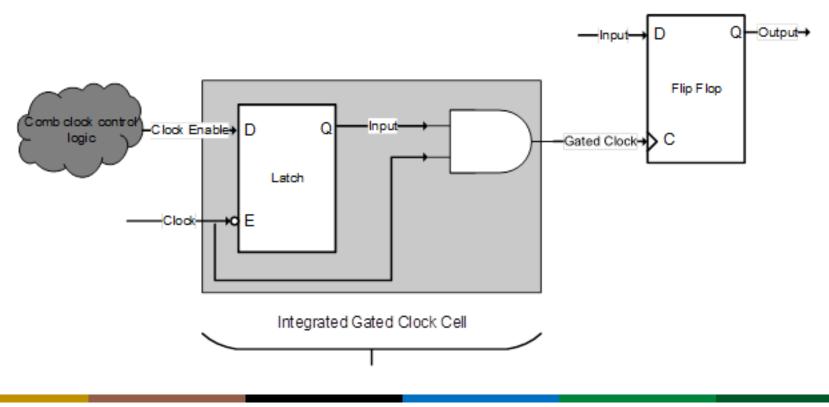

- Clock Gates

#### Part I

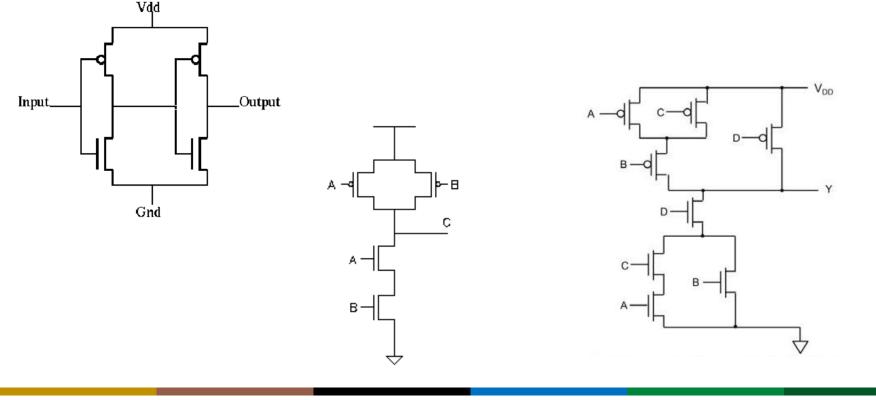

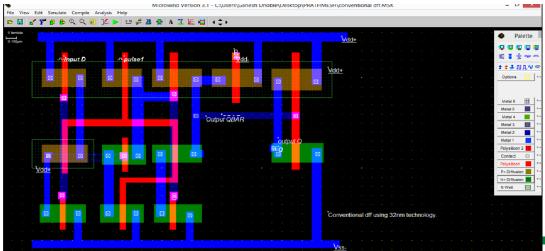

#### Design DFF, DFFRS standard cells

- Create stick diagram

- Create layout

- Magic or

- Microwind or

- Cadence IC (Virtuoso) Design Suite or

- Synopsys Custom Compiler

#### Part I

#### Design XOR/XNOR standard cells

- Create stick diagram

- Create layout

- Magic or

- Microwind or

- Cadence IC (Virtuoso) Design Suite or

- Synopsys Custom Compiler

Part I

- Layout Extraction

- Create SPICE netlist

- Verify functionality of all aforementioned standard cells

- SPICE simulation

- How?

#### Bonus I

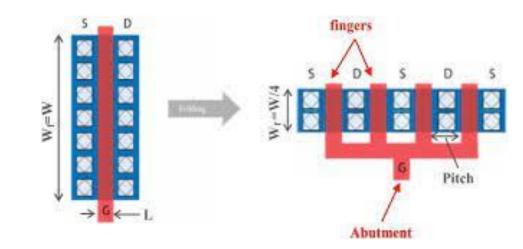

#### Design, extract and verify X1, X4 and X12 cells

- What is "drive"?

- Differences?

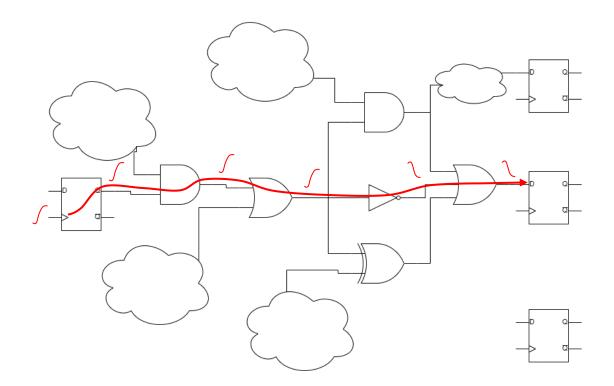

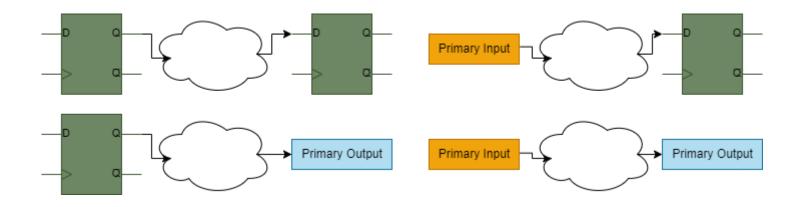

## **Timing Paths**

- Timing paths determine the Performance of our design

- Clock frequency

## **Timing Paths**

- Four types

- From Sequential Element to Sequential Element

- From Sequential Element to Primary Output

- From Primary Output to Sequential Element

- From Primary Input to Primary Output

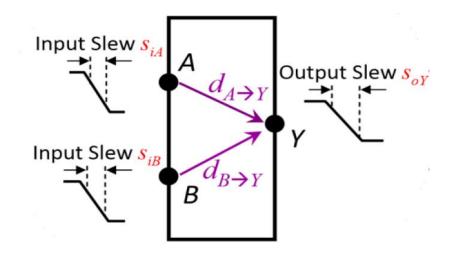

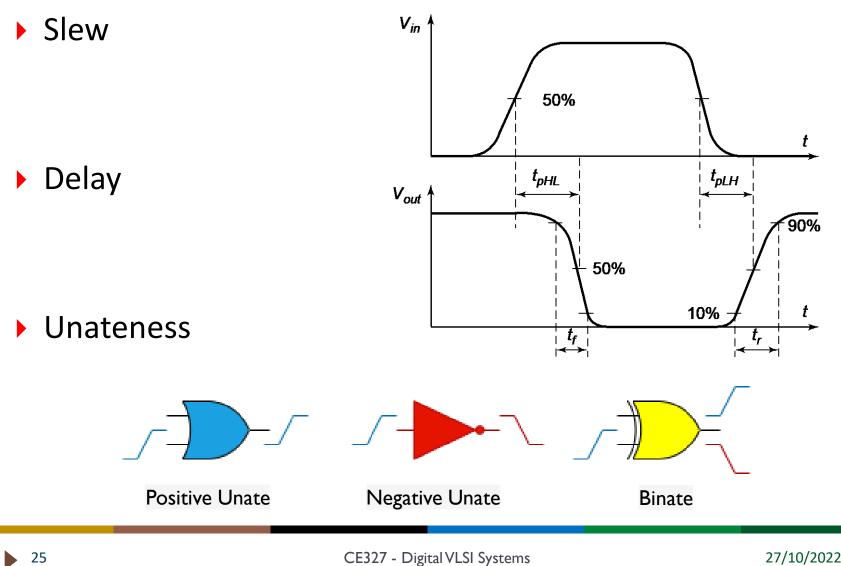

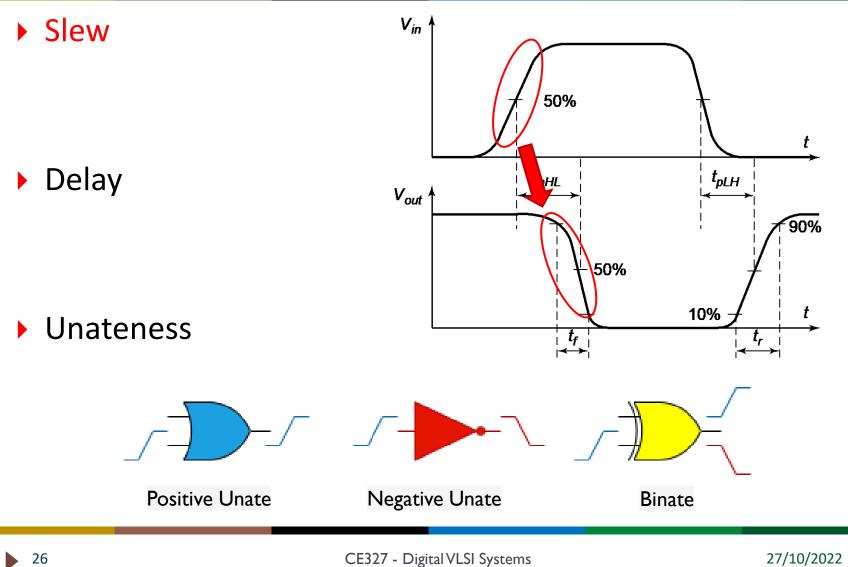

- Describe timing information from component's input to component's output

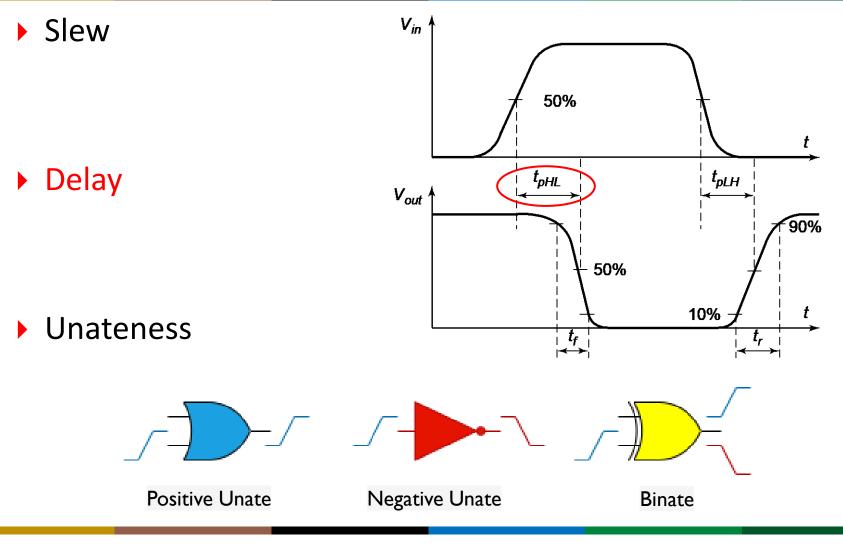

- Slew

- Delay

- Unateness

#### SPICE

- SPICE simulates the design at the device level and measures the required timing information

- Multiple SPICE tools exist

- ng-spice

- Synopsys HSPICE

- Cadence Spectre

#### SPICE vs STA

## Spice

#### Pros

- Accuracy

- Models all electrical phenomena

# **Static Timing Analysis**

#### Pros

- Orders of magnitude faster than SPICE

- Vectorless

#### Cons

- Time consuming

- Nowadays digital designs consist of million gates

- Requires input vectors

- Cons

- Inflicts Pessimism

- Circuits are DAG

- Incompatible with most analog circuits

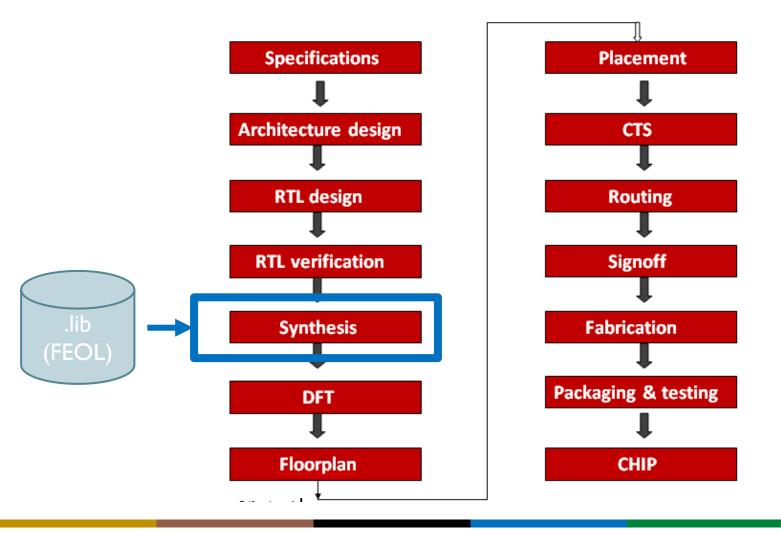

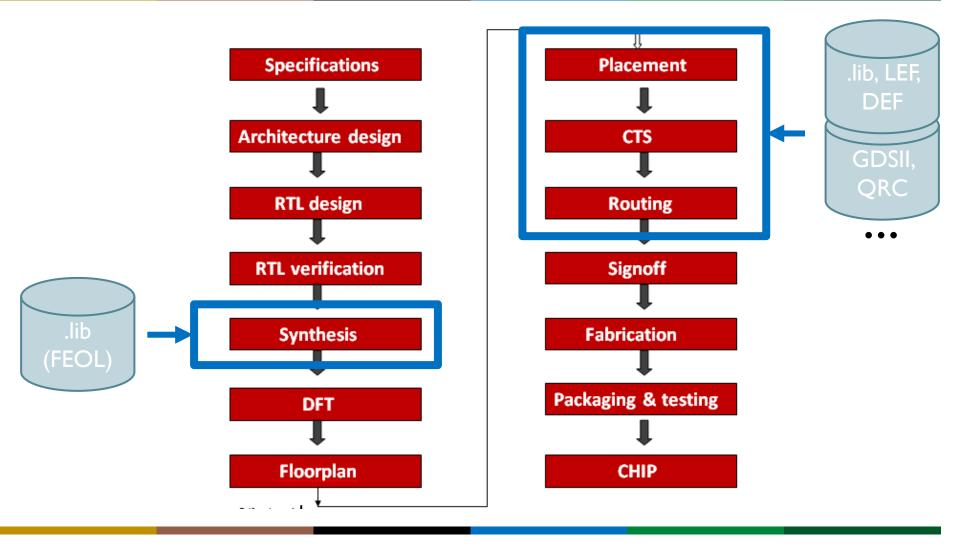

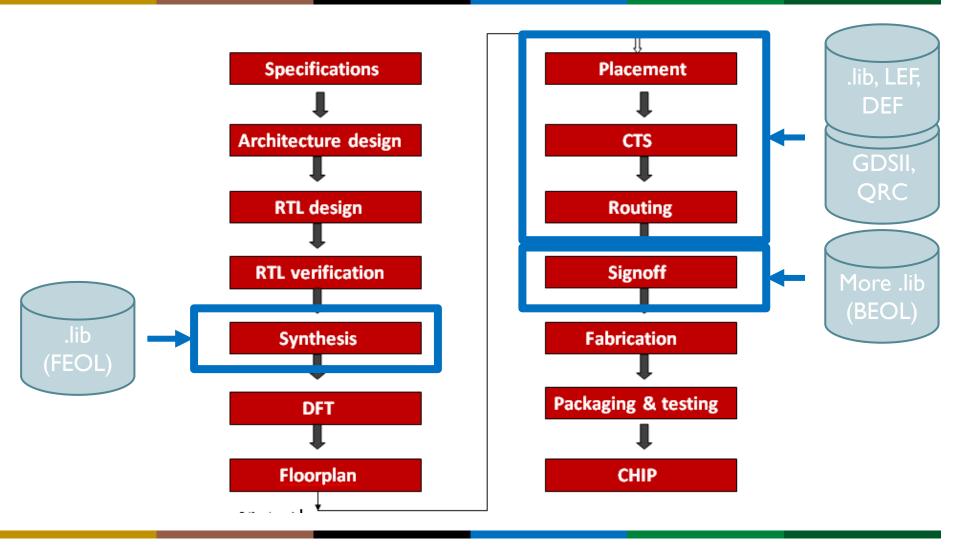

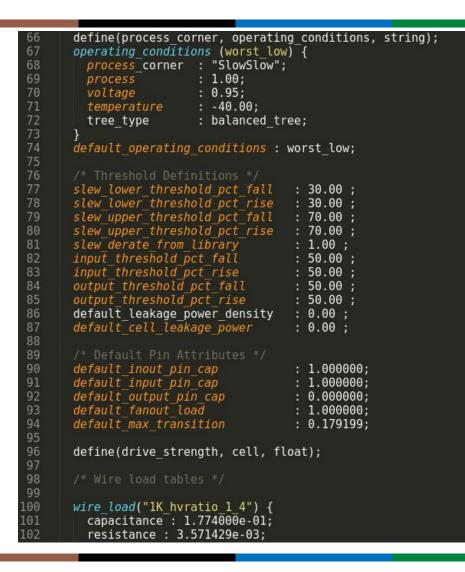

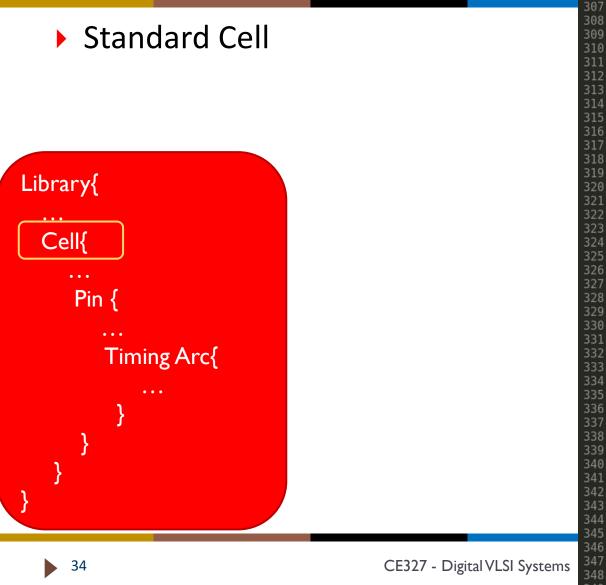

## From SPICE to STA

- We use SPICE to characterize standard cells

- Build standard cells layout

- Perform SPICE Simulation for multiple vectors (cases)

- Store measurement data in file

- Liberty File (.lib)

- A library of standard cells is created

- Then STA is applicable on any design consisted of these standard cells

- Use .lib file to estimate all cells timing information

- Perform all timing checks

- Worst case analysis (setup, recovery)

- Best case analysis (hold, removal)

- Dual mode analysis

- Multi-Mode Multi-Corner (MMMC)

- Verify no timing violations occur

| 27       | * Spice engine                     | : Nanspice v2011.01-HR04-2011-01-19-1102050200                         |

|----------|------------------------------------|------------------------------------------------------------------------|

| 28       | * Liberty export type              | : conditional                                                          |

| 29       |                                    |                                                                        |

| 30       | * Characterization Corner          | : worst_low                                                            |

| 31       | * Process                          | : SlowSlow                                                             |

| 32       | * Process<br>* Temperature         | ; -40C                                                                 |

| 33       | * Voltage                          | : 0.95V                                                                |

| 34       |                                    |                                                                        |

| 35       |                                    |                                                                        |

| 36       |                                    |                                                                        |

| 37<br>38 | library (NangateOpenCellLi         | brary) {                                                               |

| 39       | /* Documentation Attribu           | tes */                                                                 |

| 40       | date                               | : "Thu 10 Feb 2011, 18:11:08";                                         |

| 41       | revision                           | : "revision 1.0";                                                      |

| 42       | comment                            | : "Copyright (c) 2004-2011 Nangate Inc. All Rights Reserved.";         |

| 43       |                                    | 이 이 가슴에 가슴에 가슴에 가슴에 있었다. 이 같아요? 아직은 것 바람이라 가슴에 있다. 아직에게 가지 않는 것이다.<br> |

| 44       | /* General Attributes */           |                                                                        |

| 45       | technology                         | (cmos);                                                                |

| 46       |                                    | : table_lookup;                                                        |

| 47       | delay_model<br>in_place_swap_mode  | : match footprint;                                                     |

| 48       | library features                   | (report delay calculation, report power calculation);                  |

| 49       |                                    |                                                                        |

| 50       | /* Units Attributes */             |                                                                        |

| 51       | time_unit                          | : "lns";                                                               |

| 52       | leakage_power_unit                 | : "lnW";                                                               |

| 53       | voltage unit                       | : "1V";                                                                |

| 54       | current_unit                       | : "1mA";                                                               |

| 55       | pulling_resistance_unit            |                                                                        |

| 56       | <pre>capacitive_load_unit</pre>    | (1,ff);                                                                |

| 57       |                                    |                                                                        |

| 58       | <pre>/* Operation Conditions</pre> |                                                                        |

| 59       | nom_process                        | : 1.00;                                                                |

| 60       | nom_temperature                    |                                                                        |

| 61       | nom_voltage                        | : 0.95;                                                                |

| 62       |                                    |                                                                        |

| 63       | <pre>voltage_map (VDD,0.95);</pre> |                                                                        |

| 64       | <pre>voltage_map (VSS,0.00);</pre> |                                                                        |

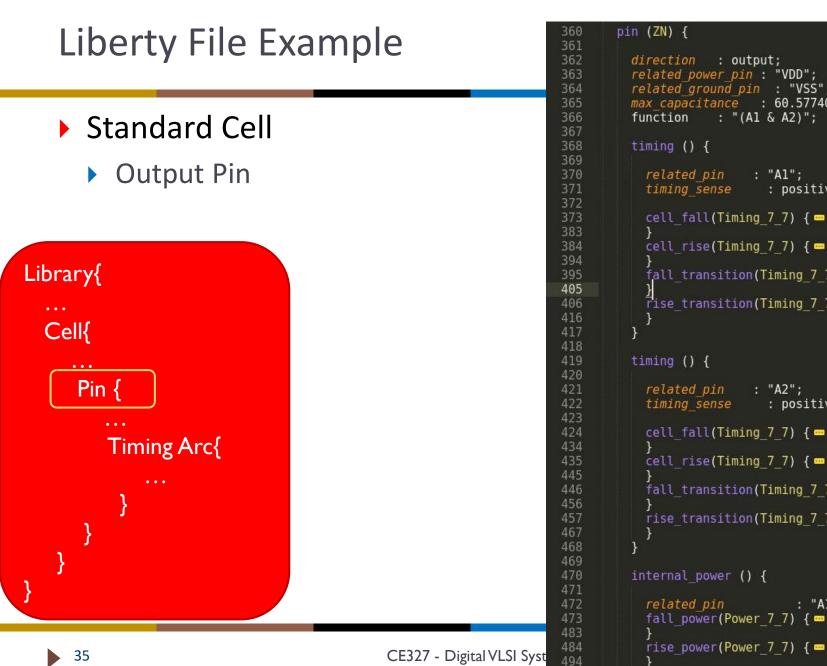

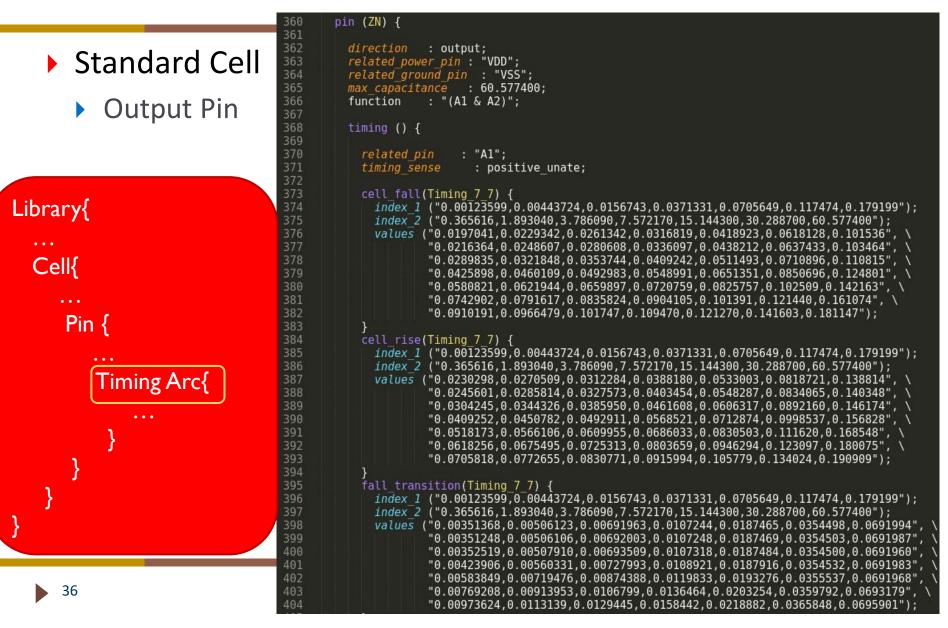

#### cell (AND2 X1) { drive strength : 1; : 1.064000; area pg pin(VDD) { voltage name : VDD; : primary power; pg type } pg pin(VSS) { voltage name : VSS; : primary ground; pg type } cell leakage power : 5.607332; leakage power () { when : "!A1 & !A2"; value : 4.987623; leakage power () { when : "!A1 & A2"; : 7.256641: value leakage power () : "A1 & !A2"; when value : 4.689846; leakage power () { : "A1 & A2"; when value : 5.495218; } pin (A1) { direction : input; : "VDD"; related power pin related ground pin : "VSS"; capacitance : 0.863124; fall capacitance : 0.825939; rise capacitance : 0.863124;

#### : output; related power pin : "VDD"; related ground pin : "VSS"; max capacitance : 60.577400; : "(A1 & A2)"; : "A1"; : positive unate; cell fall(Timing 7 7) { 📟 cell rise(Timing 7 7) { 📟 fall transition(Timing 7 7) { 🚥 rise transition(Timing 7 7) { 🚥 : "A2"; : positive unate; cell fall(Timing 7 7) { ---fall transition(Timing 7 7) { ---rise transition(Timing 7 7) { ---internal power () { : "A1"; fall power(Power 7 7) { 🚥

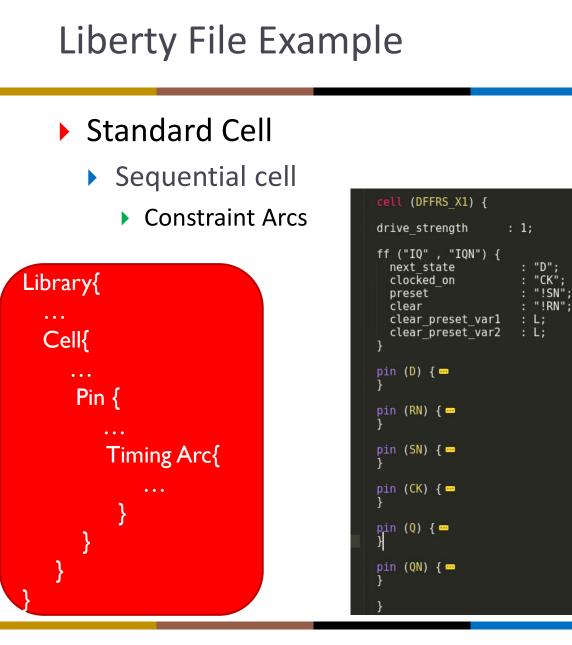

cell (DFFRS X1) { drive strength : 1; ff ("IQ" , "IQN") { : "D": next state clocked on : "CK"; : "!SN"; preset clear : "!RN"; : L; clear preset var1 clear preset var2 : L; pin (D) { direction : input; related power pin : "VDD"; related ground pin : "VSS"; capacitance : 1.090003; fall capacitance : 1.024518; rise capacitance : 1.090003; timing () { : "CK"; related pin timing type : hold rising; : "RN & SN"; when : "RN AND SN === 1'b1"; sdf cond rise constraint(Hold 3 3) { ---timing () { : "CK"; related pin timing type : setup rising; : "RN & SN"; when : "RN AND SN === 1'b1"; sdf cond fall constraint(Setup 3 3) { ---rise constraint(Setup 3 3) { •• internal power () {

}

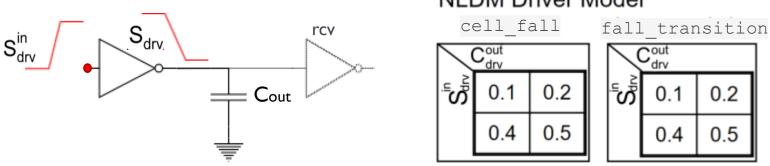

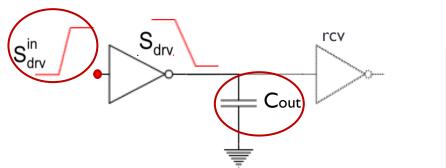

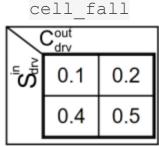

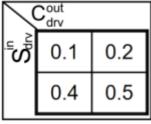

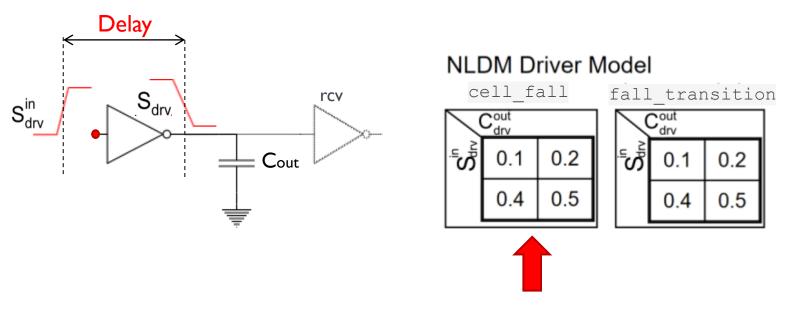

- Output slew and delay calculation using .lib data

- Calculation is performed based on

- Input slew

- **Output load**

#### NLDM Driver Model

∽out drv 0.2 0.1 0.5 0.4

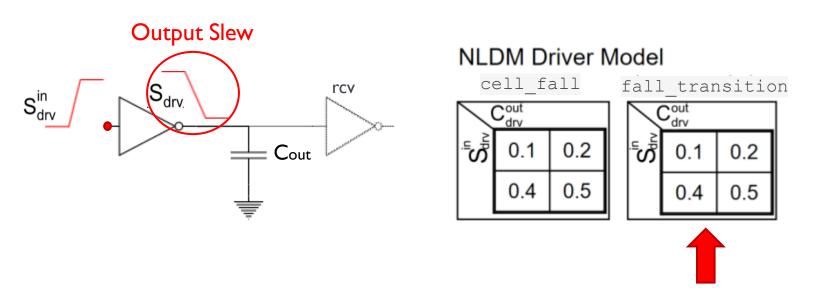

- Output slew and delay calculation using .lib data

- Calculation is performed based on

- Input slew

- Output load

#### NLDM Driver Model

- Output slew and delay calculation using .lib data

- Calculation is performed based on

- Input slew

- Output load

- Output slew and delay calculation using .lib data

- Calculation is performed based on

- Input slew

- Output load

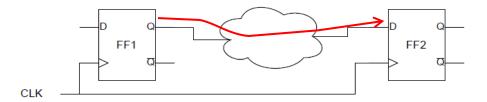

# **Timing Checks**

- Timing constraints are imposed to Sequential std. cells

- To ensure correct functionality

- Such constraints are Setup, Hold, Recovery and Removal time

- STA tools perform timing checks to ensure no violations will happen

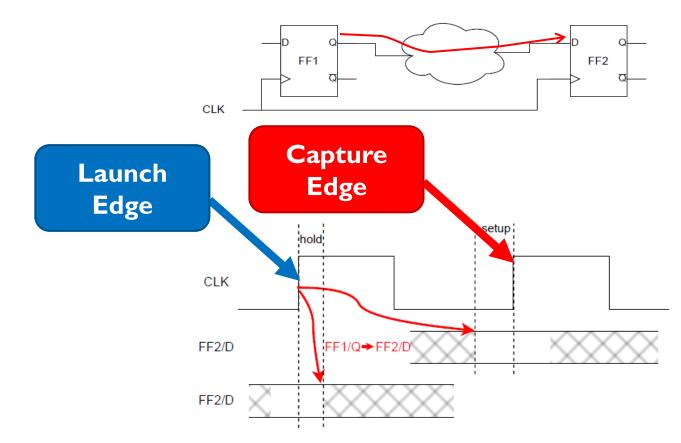

#### Data Launch and Capture

27/10/2022

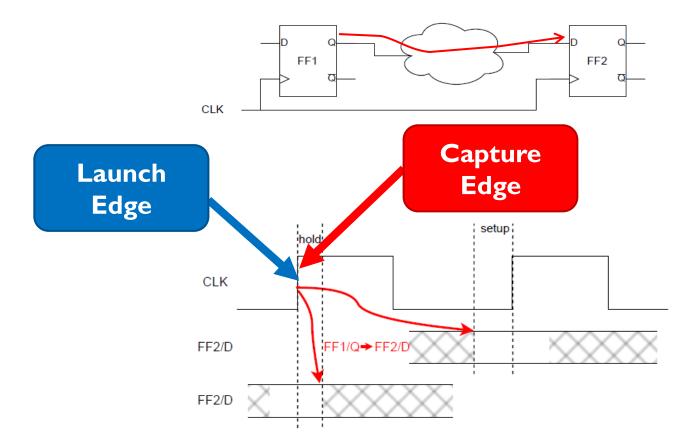

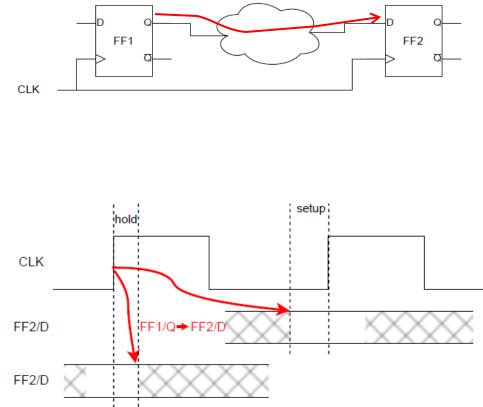

### Data Launch and Capture

For Setup Timing Check:

### Data Launch and Capture

For Hold Timing Check:

27/10/2022

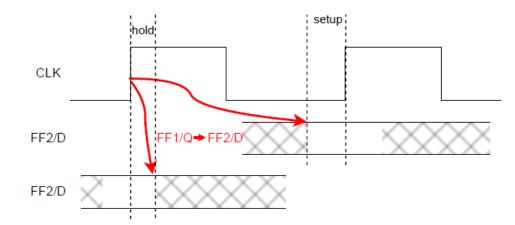

### **Timing Checks**

#### Setup timing check

Data must arrive to path endpoint, before a specific time margin from next clock active edge

#### Hold timing check

Data must remain stable at path endpoint, for a specific time margin after the same clock active edge, which triggered data launch

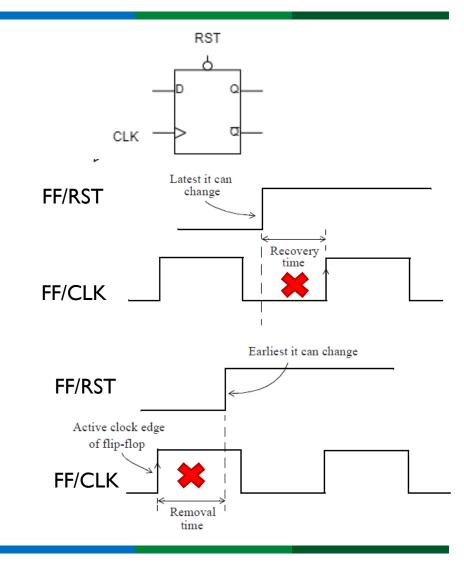

## **Timing Checks**

#### Recovery timing check

- Reset should arrive before a specific time margin from next active clock edge

- Resembles Setup timing check

- Removal timing check

- Reset should arrive after a specific time margin from last active clock edge

- Resembles Hold timing check

### Part II

- Create C/C++/Python/Bash program

- Use extracted SPICE deck (magic, ext2spice) from Part I

- Run SPICE for multiple stimulus and load combinations

- 1 run per input slew, output load pair

- Measure delay and slew

- Store measurement data

- Tools:

- ng-spice/Xyce/HSPICE/Spectre

- Calculate setup, hold, recovery, removal times for Flip-Flops

- Trial and error methodology

- Write measurement data to your own custom Liberty File (.lib)

- You will be provided with a template Liberty File

- You will only need to write specific fields, NOT the entire file from scratch

#### Verilog is one of the 2 most widespread Hardware Description Languages (HDLs)

# Verilog

- Verilog is one of the 2 most widespread Hardware Description Languages (HDLs)

- The other one being VHDL

# Verilog

- Verilog is one of the 2 most widespread Hardware Description Languages (HDLs)

- The other one being VHDL

- We will only use it in its Gate-Level Netlist form

- Wires

- Standard cell instantiations

- I/O ports and top module declaration

```

module counter_DW01_inc_0 ( A, SUM );

input [7:0] A;

output [7:0] SUM;

wire [7:2] carry;

HAJIX0 U1 1 6 ( .A(A[6]), .B(carry[6]), .C0(carry[7]), .S(SUM[6]) );

HAJIX0 U1 1 5 ( .A(A[5]), .B(carry[5]), .C0(carry[6]), .S(SUM[5]) );

HAJIX0 U1 1 4 ( .A(A[4]), .B(carry[4]), .C0(carry[6]), .S(SUM[4]) );

HAJIX0 U1 1 3 ( .A(A[4]), .B(carry[4]), .C0(carry[5]), .S(SUM[4]) );

HAJIX0 U1 1 3 ( .A(A[3]), .B(carry[3]), .C0(carry[4]), .S(SUM[3]) );

HAJIX0 U1 1 2 ( .A(A[2]), .B(carry[2]), .C0(carry[4]), .S(SUM[2]) );

HAJIX0 U1 1 1 ( .A(A[1]), .B(A[0]), .C0(carry[2]), .S(SUM[1]) );

INVJIX0 U1 ( .A(A[0]), .Q(SUM[0]) );

E02JIX0 U2 ( .A(carry[7]), .B(A[7]), .Q(SUM[7]) );

```

### Part III

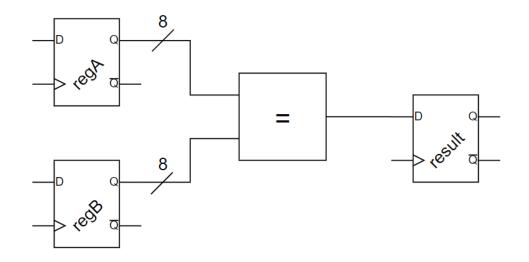

- Use the std. cells you created and characterized in Parts I & II and create a Verilog module which contains

- 2 8-bit registers

- A comparator which compares the above registers

- I register to store the comparator result

#### Part III

- Use the std. cells you created and characterized in Parts I & II and create a Verilog module which contains

- 2 8-bit registers

- A comparator which compares the above registers

- I register to store the comparator result

### Part III

- Create Verilog `specify' blocks for the std. cells you created

- Create Testbench and make sure your design is functioning properly

- Tools: Modelsim

- Use an STA engine to analyze timing

- We will provide you with the script

- Tools:

- OpenROAD OpenSTA

- Synopsys PrimeTime

- Cadence Tempus

- Find the critical path of your design

### Bonus II

- Use the higher drive std. cells you created in Bonus I

- Optimize your design for highest possible performance

- Try to perform area recovery

- Comment on your thought process and efforts to achieve the above